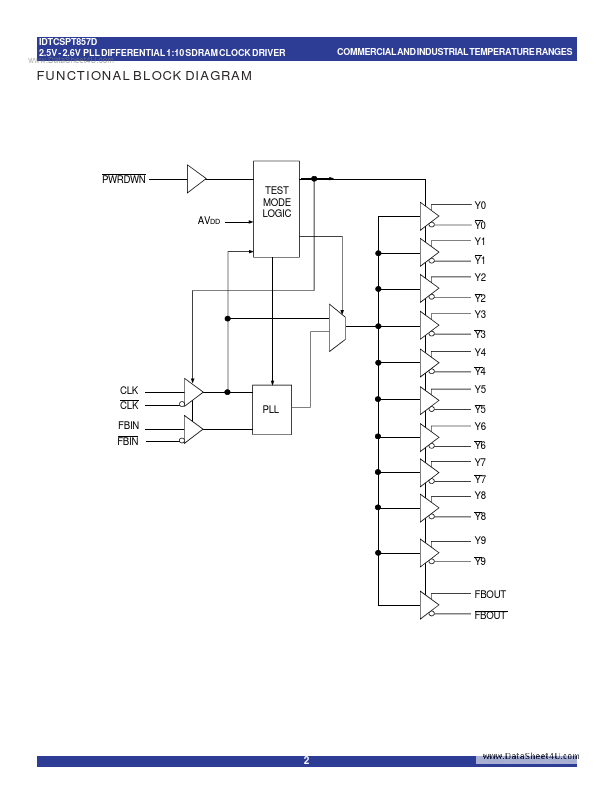

IDTCSPT857D Description

IDTCSPT857D 1 to 10 differential clock distribution Optimized for clock distribution in DDR (Double Data Rate) SDRAM applications requiring improved output crosspoint voltage Operating frequency: 60MHz to 220MHz Very low skew: <100ps for PC1600 - PC2700 <75ps for PC3200 Very low jitter:.

IDTCSPT857D Key Features

- 1 to 10 differential clock distribution

- Optimized for clock distribution in DDR (Double Data Rate) SDRAM

IDTCSPT857D Applications

- Operating frequency: 60MHz to 220MHz