IDTCSPF2510C

IDTCSPF2510C is 3.3V PHASE-LOCK LOOP CLOCK DRIVER manufactured by Integrated Device Technology.

..

IDTCSPF2510C 3.3V PHASE-LOCK LOOP CLOCK DRIVER

0ºC TO 85ºC TEMPERATURE RANGE

3.3V PHASE-LOCK LOOP CLOCK DRIVER

Features

:

- Phase-Lock Loop Clock Distribution for Synchronous DRAM Applications

- Distributes one clock input to one bank of ten outputs

- Output enable bank control

- External feedback (FBIN) pin is used to synchronize the output to the clock input signal

- On-chip series damping resistors with each driver

- No external RC network required for PLL loop stability

- Operates at 3.3V VDD

- tpd Phase Error at 133MHz: < ±150ps

- Jitter (cycle-cycle)(peak-to-peak) at 66MHz to 133MHz: | 70 | ps

- Spread Spectrum patible

- Operating frequency 25MHz to 140MHz

- Fully conforms to PC133 specifications

- Available in 24-Pin TSSOP package

DESCRIPTION:

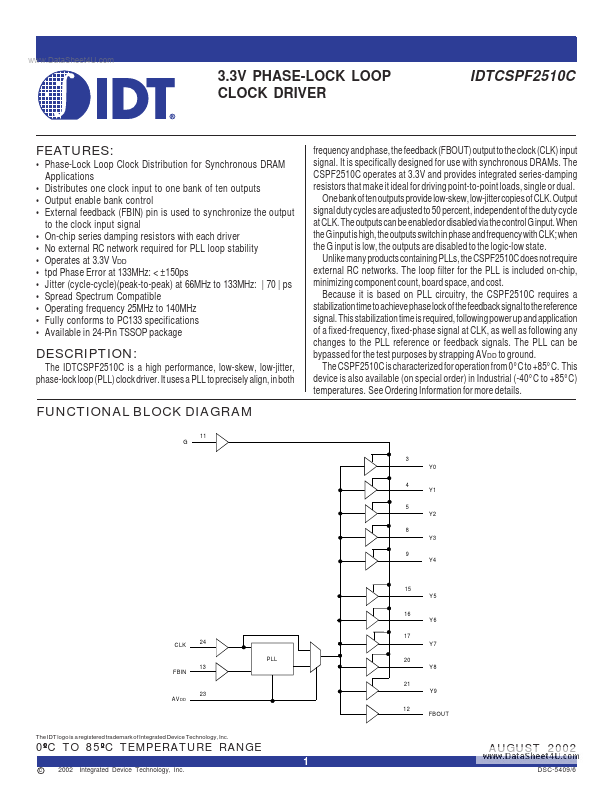

The IDTCSPF2510C is a high performance, low-skew, low-jitter, phase-lock loop (PLL) clock driver. It uses a PLL to precisely align, in both frequency and phase, the feedback (FBOUT) output to the clock (CLK) input signal. It is specifically designed for use with synchronous DRAMs. The CSPF2510C operates at 3.3V and provides integrated series-damping resistors that make it ideal for driving point-to-point loads, single or dual. One bank of ten outputs provide low-skew, low-jitter copies of CLK. Output signal duty cycles are adjusted to 50 percent, independent of the duty cycle at CLK. The outputs can be enabled or disabled via the control G input. When the G input is high, the outputs switch in phase and frequency with CLK; when the G input is low, the outputs are disabled to the logic-low state. Unlike many products containing PLLs, the CSPF2510C does not require external RC networks. The loop filter for the PLL is included on-chip, minimizing ponent count, board space, and cost. Because it is based on PLL circuitry, the CSPF2510C requires a stabilization time to achieve phase lock of the feedback signal to the reference signal. This stabilization time is required,...