IDTCSPU877A

IDTCSPU877A is 1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER manufactured by Integrated Device Technology.

..

IDTCSPU877A 1.8V PLL DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER

MERCIAL TEMPERATURE RANGE

1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER

Features

: DESCRIPTION:

- 1 to 10 differential clock distribution

- Optimized for clock distribution in DDR2 (Double Data Rate) SDRAM applications

- Operating frequency: 125MHz to 270MHz

- Very low skew: ≤40ps

- Very low jitter: ≤40ps

- 1.8V AVDD and 1.8V VDDQ

- CMOS control signal input

- Test mode enables buffers while disabling PLL

- Low current power-down mode

- Tolerant of Spread Spectrum input clock

- Available in 52-Ball VFBGA and 40-pin MLF packages

APPLICATIONS:

- Meets or exceeds JEDEC standard 82.8 for registered DDR2 clock driver

- Along with SSTU32864/65/66, DDR2 register, provides plete solution for DDR2 DIMMs

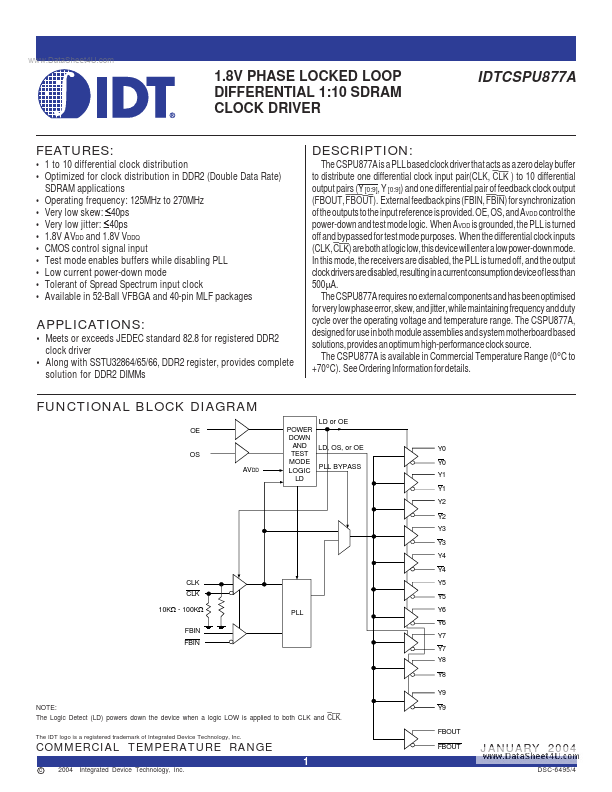

The CSPU877A is a PLL based clock driver that acts as a zero delay buffer to distribute one differential clock input pair(CLK, CLK ) to 10 differential output pairs (Y [0:9], Y [0:9]) and one differential pair of feedback clock output (FBOUT, FBOUT). External feedback pins (FBIN, FBIN) for synchronization of the outputs to the input reference is provided. OE, OS, and AVDD control the power-down and test mode logic. When AVDD is grounded, the PLL is turned off and bypassed for test mode purposes. When the differential clock inputs (CLK, CLK) are both at logic low, this device will enter a low power-down mode. In this mode, the receivers are disabled, the PLL is turned off, and the output clock drivers are disabled, resulting in a current consumption device of less than 500µA. The CSPU877A requires no external ponents and has been optimised for very low phase error, skew, and jitter, while maintaining frequency and duty cycle over the operating voltage and temperature range. The CSPU877A, designed for use in both module assemblies and system motherboard based solutions, provides an optimum high-performance clock source. The CSPU877A is available in...