IS61NSCS25672 Overview

Key Specifications

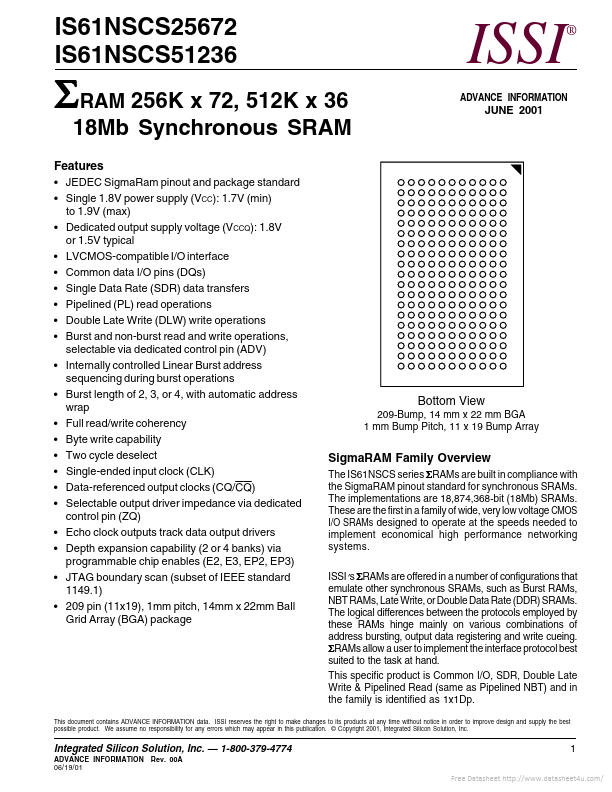

Package: BGA

Operating Voltage: 1.8 V

Max Voltage (typical range): 1.9 V

Min Voltage (typical range): 1.7 V

Key Features

- JEDEC SigmaRam pinout and package standard

- Single 1.8V power supply (VCC): 1.7V (min) to 1.9V (max)

- Dedicated output supply voltage (VCCQ): 1.8V or 1.5V typical

- LVCMOS-compatible I/O interface

- Common data I/O pins (DQs)