C5002

C5002 is Low Skew Muliple Frequency PCI Clock Generator with EMI Reducing SSCG manufactured by International.

Features

- -

- -

- -

- -

- -

- - Produces PCI output clocks that are individually selectable for 33.3 or 66.6 MHz under SMBus or strapping control. Separate output buffer power supply for reduced noise, crosstalk and jitter. input clock frequency standard 14.31818 MHz Output clocks frequency individually selectable via SMBus or hardware bi-directional pin strapping. SSCG EMI reduction at 1.0% width Individual clock disables via SMBus control All output clocks skewed within a 500 p S window Cycle to Cycle jitter ± 250 p S Output duty cycle is automatically 50% (±10%) adjusted Clock feed through mode and OE pins for logic testing Glitchless clock enabling and disabling transitions 28-pin TSSOP or SSOP package

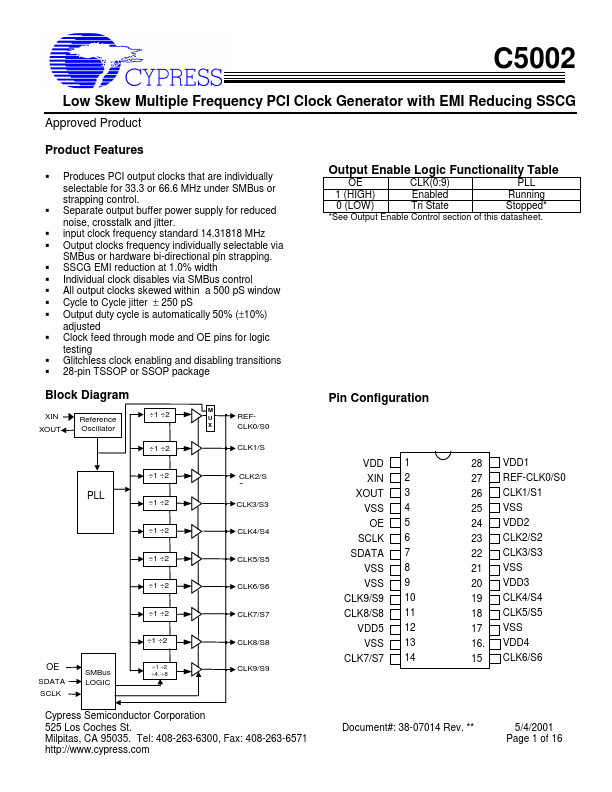

Output Enable Logic Functionality Table

OE 1 (HIGH) 0 (LOW) CLK(0:9) Enabled Tri State PLL Running Stopped-

- See Output Enable Control section of this datasheet.

Block Diagram

XIN XOUT Reference Oscillator ÷1 ÷2

Pin Configuration

REFCLK0/S0 CLK1/S

÷1 ÷2 ÷1 ÷2

CLK2/S 2 CLK3/S3 CLK4/S4

1 2 3 4 5 6 7 8 9 10 11 12 13 14

28 27 26 25 24 23 22 21 20 19 18 17 16. 15

VDD1 REF-CLK0/S0 CLK1/S1 VSS VDD2 CLK2/S2 CLK3/S3 VSS VDD3 CLK4/S4 CLK5/S5 VSS VDD4 CLK6/S6

XIN XOUT VSS OE SCLK SDATA VSS VSS CLK9/S9 CLK8/S8 VDD5 VSS CLK7/S7

÷1 ÷2 ÷1 ÷2 ÷1 ÷2 ÷1 ÷2 ÷1 ÷2 ÷1 ÷2

CLK5/S5 CLK6/S6

CLK7/S7

CLK8/S8 CLK9/S9

SDATA SCLK

SMBus LOGIC

÷1 ÷2 ÷4, ÷8

Cypress Semiconductor Corporation 525 Los Coches St. Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571 http://.cypress.

Document#: 38-07014 Rev.

- -

5/4/2001 Page 1 of 16

Low Skew Multiple Frequency PCI Clock Generator with EMI Reducing SSCG

Approved Product Pin Description

Pin Number 2 Pin Name XIN PWR VDDA I/O I Description

This pin is the connection point for the devices Loop reference frequency. This may be either a CMOS 3.3 volt reference clock or the output of an external crystal. A nominal 14.31818 MHz frequency must be supplied to obtain the frequencies listed on this data sheet This...