IP2003A

Features

:

Integrated Power Semiconductors, Drivers & Passives

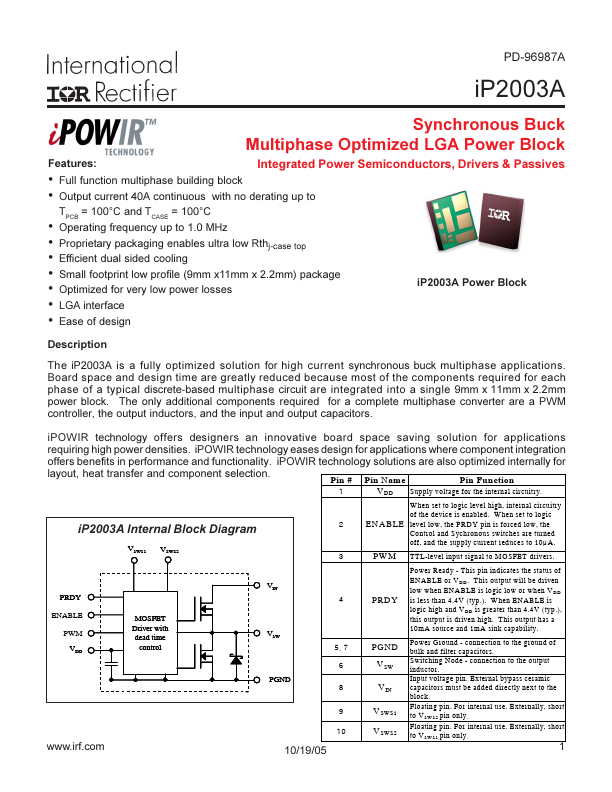

Full function multiphase building block Output current 40A continuous with no derating up to TPCB = 100°C and TCASE = 100°C Operating frequency up to 1.0 MHz Proprietary packaging enables ultra low Rthj-case top Efficient dual sided cooling Small footprint low profile (9mm x11mm x 2.2mm) package Optimized for very low power losses LGA interface Ease of design i P2003A Power Block

Description

The i P2003A is a fully optimized solution for high current synchronous buck multiphase applications. Board space and design time are greatly reduced because most of the ponents required for each phase of a typical discrete-based multiphase circuit are integrated into a single 9mm x 11mm x 2.2mm power block. The only additional ponents required for a plete multiphase converter are a PWM controller, the output inductors, and the input and output capacitors. i POWIR technology offers designers an innovative board space...