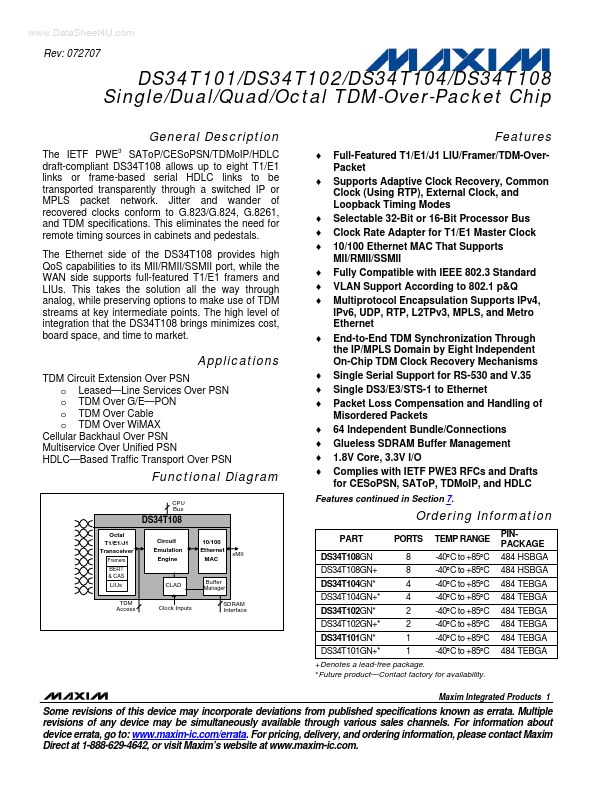

DS34T102 Description

The IETF PWE SAToP/CESoPSN/TDMoIP/HDLC draft-pliant DS34T108 allows up to eight T1/E1 links or frame-based serial HDLC links to be transported transparently through a switched IP or MPLS packet network. Jitter and wander of recovered clocks conform to G.823/G.824, G.8261, and TDM specifications. This eliminates the need for remote timing sources in cabinets and pedestals.