Datasheet Summary

Micrel, Inc.

DUAL PARITY CHECKER/ GENERATOR

Features

DESCRIPTION s Max. propagation delay of 2200ps s IEE min. of

- 70mA s Industry standard 100K ECL levels s Extended supply voltage option:

VEE =

- 4.2V to

- 5.5V s Voltage and temperature pensation for improved noise immunity s Internal 75kΩ input pull-down resistors s 15% faster than Fairchild 300K s Approximately 30% lower power than Fairchild 300K s Function and pinout patible with Fairchild F100K s Available in 28-pin PLCC package

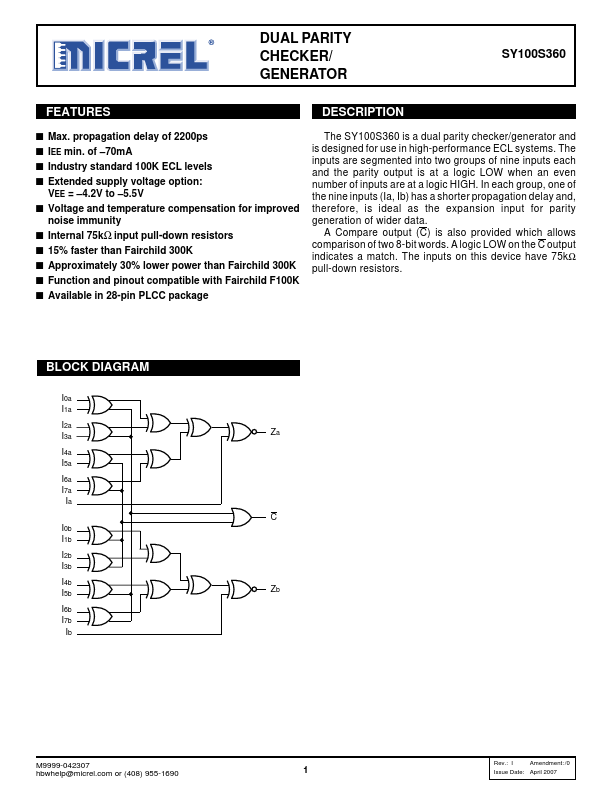

The SY100S360 is a dual parity checker/generator and is designed for use in high-performance ECL systems. The inputs are segmented into two groups of nine inputs each and the...