MT9041

MT9041 is Multiple Output Trunk PLL manufactured by Mitel Networks Corporation.

®

Multiple Output Trunk PLL Advance Information

Features

- Provides T1 and E1 clocks, and ST-BUS/GCI framing signals locked to an input reference of either 8 k Hz (frame pulse), 1.544 MHz (T1), or 2.048 MHz (E1) Meets AT & T TR62411 and ETSI ETS 300 011 specifications for a 1.544 MHz (T1), or 2.048 MHz (E1) input reference Typical unfiltered intrinsic output jitter is 0.013 UI peak-to-peak Jitter attenuation of 15 d B @ 10 Hz, 34 d B @ 100 Hz and 50 d B @ 5 to 40 k Hz Low power CMOS technology

ISSUE 1

May 1995

Ordering Information MT9041AP 28 Pin PLCC -40 °C to +85 °C

- Description

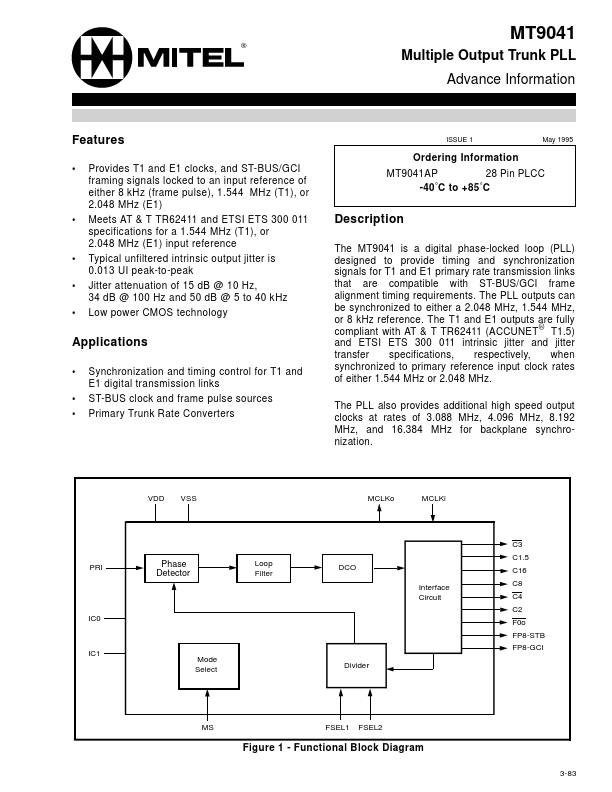

The MT9041 is a digital phase-locked loop (PLL) designed to provide timing and synchronization signals for T1 and E1 primary rate transmission links that are patible with ST-BUS/GCI frame alignment timing requirements. The PLL outputs can be synchronized to either a 2.048 MHz, 1.544 MHz, or 8 k Hz reference. The T1 and E1 outputs are fully pliant with AT & T TR62411 (ACCUNET® T1.5) and ETSI ETS 300 011 intrinsic jitter and jitter transfer specifications, respectively, when synchronized to primary reference input clock rates of either 1.544 MHz or 2.048 MHz. The PLL also provides additional high speed output clocks at rates of 3.088 MHz, 4.096 MHz, 8.192 MHz, and 16.384 MHz for backplane synchronization.

- -

- Applications

- -

- Synchronization and timing control for T1 and E1 digital transmission links ST-BUS clock and frame pulse sources Primary Trunk Rate Converters

MCLKo

MCLKi

C3 PRI

Phase Detector

Loop Filter

C1.5 DCO Interface Circuit C16 C8 C4 C2 F0o FP8-STB FP8-GCI

IC0

IC1

Mode Select

Divider

FSEL1

FSEL2

Figure 1

- Functional Block Diagram

3-83

IC0 VSS RST FSEL1 FSEL2

Advance...