PDSP16116MC

16 by 16 Bit Complex Multiplier (Zarlink Semiconductor)

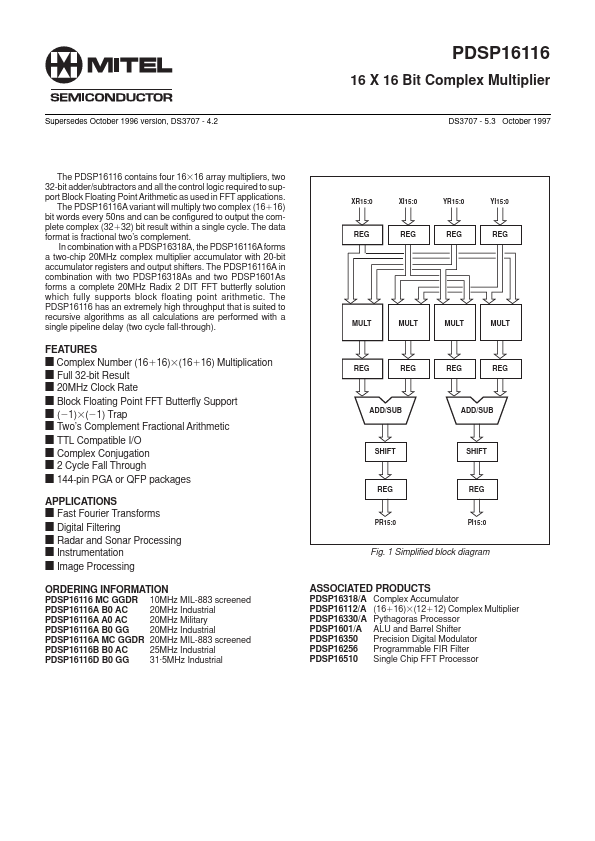

PDSP16116

16 X 16 Bit Complex Multiplier (Mitel Networks Corporation)

PDSP16116

16 by 16 Bit Complex Multiplier (Zarlink Semiconductor)

PDSP16116A

16 by 16 Bit Complex Multiplier (Zarlink Semiconductor)

PDSP16116AA0AC

16 X 16 Bit Complex Multiplier (Mitel Networks Corporation)

PDSP16116AB0AC

16 X 16 Bit Complex Multiplier (Mitel Networks Corporation)

PDSP16116AB0GG

16 X 16 Bit Complex Multiplier (Mitel Networks Corporation)

PDSP16116AMCGGDR

16 X 16 Bit Complex Multiplier (Mitel Networks Corporation)

PDSP16116BB0AC

16 X 16 Bit Complex Multiplier (Mitel Networks Corporation)

PDSP16116DB0GG

16 X 16 Bit Complex Multiplier (Mitel Networks Corporation)