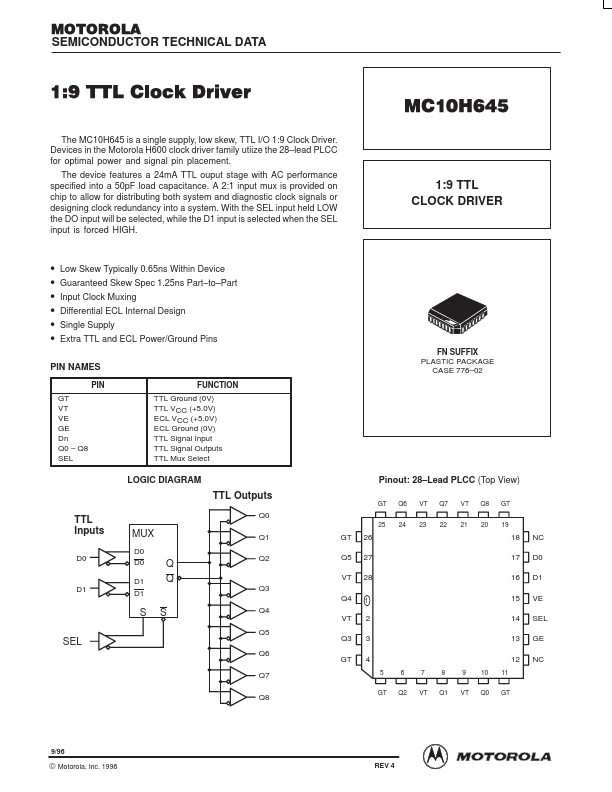

| Part | MC10H645 |

|---|---|

| Description | 1:9 TTL Clock Driver |

| Manufacturer | Motorola Semiconductor |

| Size | 105.74 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MC10H645 | onsemi | 2:1:9 TTL Clock Driver |

| MC10H642 | onsemi | 68030/040 PECL-TTL CLOCK DRIVER |

| MC10H646 | onsemi | PENTIUM MICROPROCESSOR PECL/TTL-TTL CLOCK DRIVER |

| MC10H644 | onsemi | 68030/040 PECL-TTL CLOCK DRIVER |

| MC10H640 | onsemi | PECL-TTL CLOCK DRIVER |