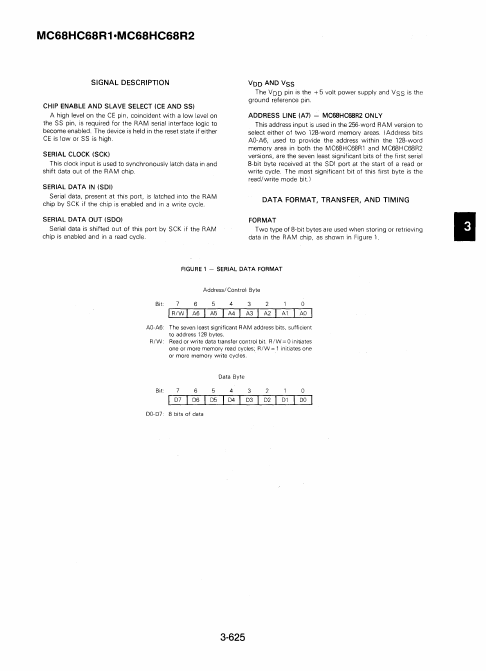

MC68HC68R2 Description

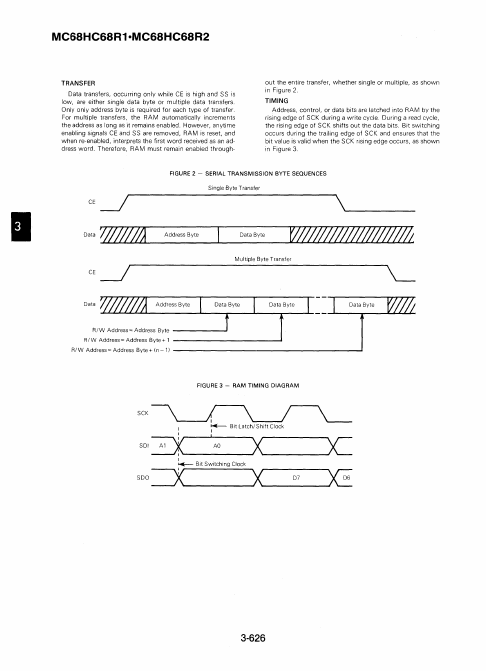

CHIP ENABLE AND SLAVE SELECT (CE AND SS) A high level on the CE pin, coincident with a low level on the SS pin, is required for the RAM serial interface logic to bee enabled. The device is held in the reset state if either CE is low or SS is high. SERIAL CLOCK (SCK) This clock input is used to synchronously latch data in and shift data out of the RAM chip.