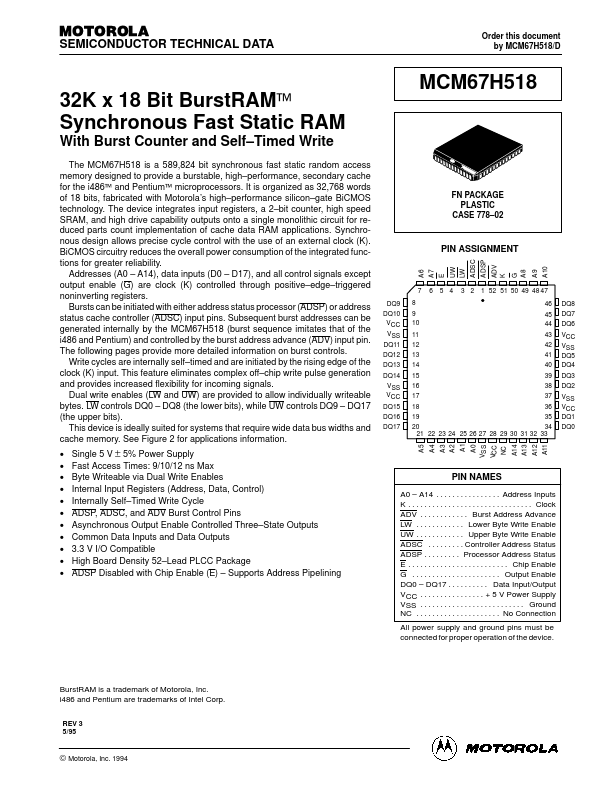

MCM67H518 Overview

Key Features

- eliminates complex off–chip write pulse generation and provides increased flexibility for incoming signals

- Dual write enables (LW and UW) are provided to allow individually writeable bytes

- LW controls DQ0 – DQ8 (the lower bits), while UW controls DQ9 – DQ17 (the upper bits)

- This device is ideally suited for systems that require wide data bus widths and cache memory

- See Figure 2 for applications information