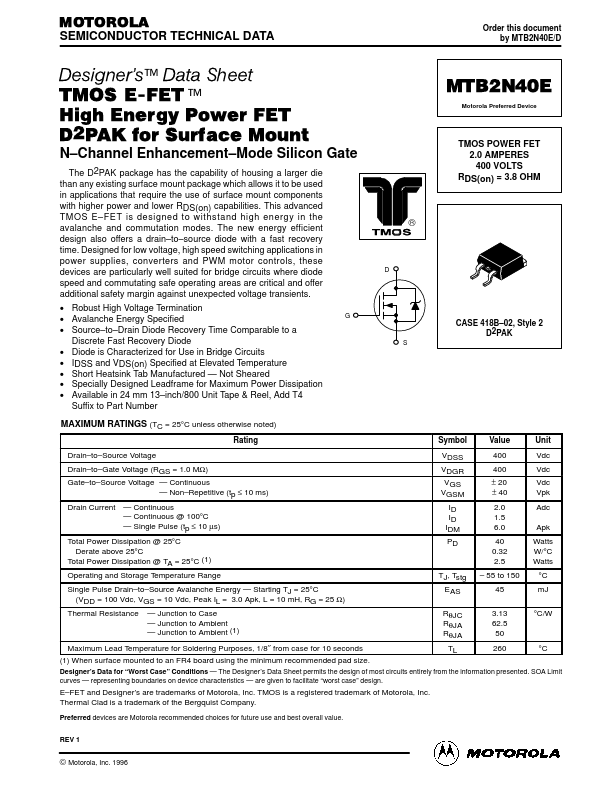

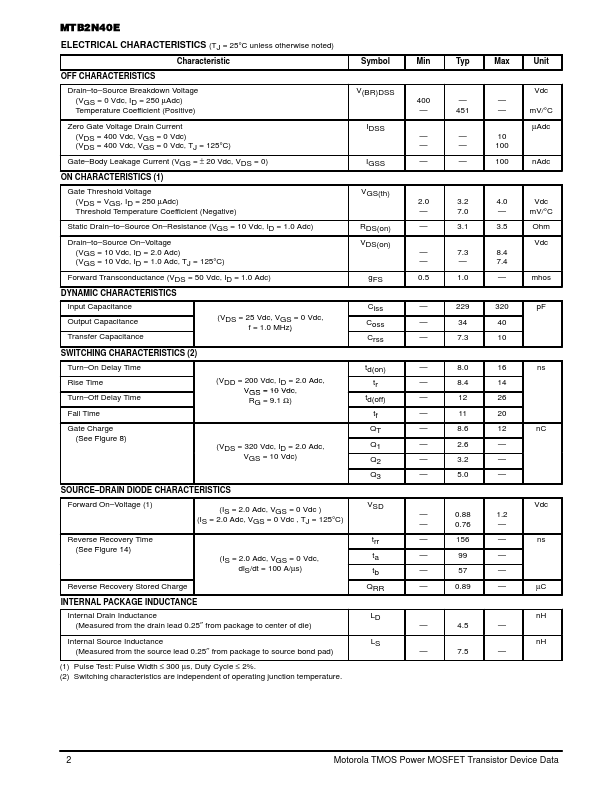

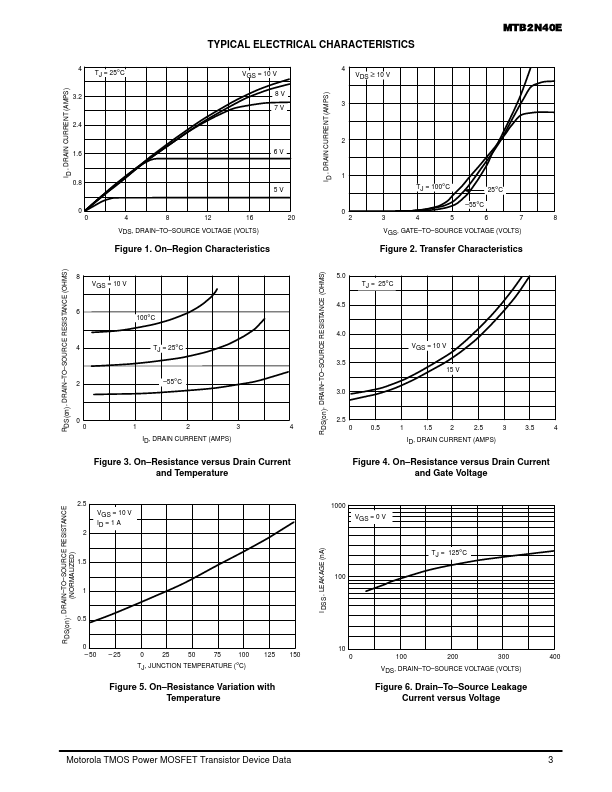

- Part: MTB2N40E

- Description: TMOS POWER FET

- Manufacturer: Motorola Semiconductor

- Size: 271.38 KB

Related Motorola Semiconductor Datasheets

| Part Number | Description |

|---|---|

| MTB2N60E | TMOS POWER FET |

| MTB20N20E | TMOS POWER FET |

| MTB23P06E | TMOS POWER FET |

| MTB23P06V | TMOS POWER FET |

| MTB29N15E | TMOS POWER FET |