UPD4482362

UPD4482362 is 8M-BIT CMOS SYNCHRONOUS FAST SRAM manufactured by NEC.

- Part of the UPD4482162 comparator family.

- Part of the UPD4482162 comparator family.

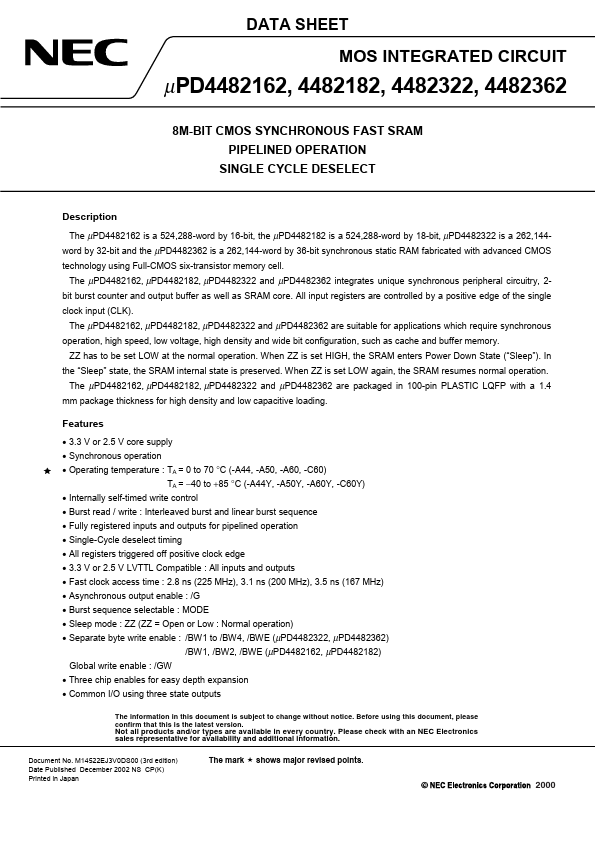

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD4482162, 4482182, 4482322, 4482362

8M-BIT CMOS SYNCHRONOUS FAST SRAM PIPELINED OPERATION SINGLE CYCLE DESELECT

Description

The µPD4482162 is a 524,288-word by 16-bit, the µPD4482182 is a 524,288-word by 18-bit, µPD4482322 is a 262,144word by 32-bit and the µPD4482362 is a 262,144-word by 36-bit synchronous static RAM fabricated with advanced CMOS technology using Full-CMOS six-transistor memory cell. The µPD4482162, µPD4482182, µPD4482322 and µPD4482362 integrates unique synchronous peripheral circuitry, 2bit burst counter and output buffer as well as SRAM core. All input registers are controlled by a positive edge of the single clock input (CLK). The µPD4482162, µPD4482182, µPD4482322 and µPD4482362 are suitable for applications which require synchronous operation, high speed, low voltage, high density and wide bit configuration, such as cache and buffer memory. ZZ has to be set LOW at the normal operation. When ZZ is set HIGH, the SRAM enters Power Down State (“Sleep”). In the “Sleep” state, the SRAM internal state is preserved. When ZZ is set LOW again, the SRAM resumes normal operation. The µPD4482162, µPD4482182, µPD4482322 and µPD4482362 are packaged in 100-pin PLASTIC LQFP with a 1.4 mm package thickness for high density and low capacitive loading.

Features

- 3.3 V or 2.5 V core supply

- Synchronous operation

- Operating temperature : TA = 0 to 70 °C (-A44, -A50, -A60, -C60) TA =

- 40 to +85 °C (-A44Y, -A50Y, -A60Y, -C60Y)

- Internally self-timed write control

- Burst read / write : Interleaved burst and linear burst sequence

- Fully registered inputs and outputs for pipelined operation

- Single-Cycle deselect timing

- All registers triggered off positive clock edge

- 3.3 V or 2.5 V LVTTL patible : All inputs and outputs

- Fast clock access time : 2.8 ns (225 MHz), 3.1 ns (200 MHz), 3.5 ns (167 MHz)

- Asynchronous output enable : /G

- Burst sequence selectable : MODE

- Sleep mode : ZZ (ZZ = Open or Low : Normal...