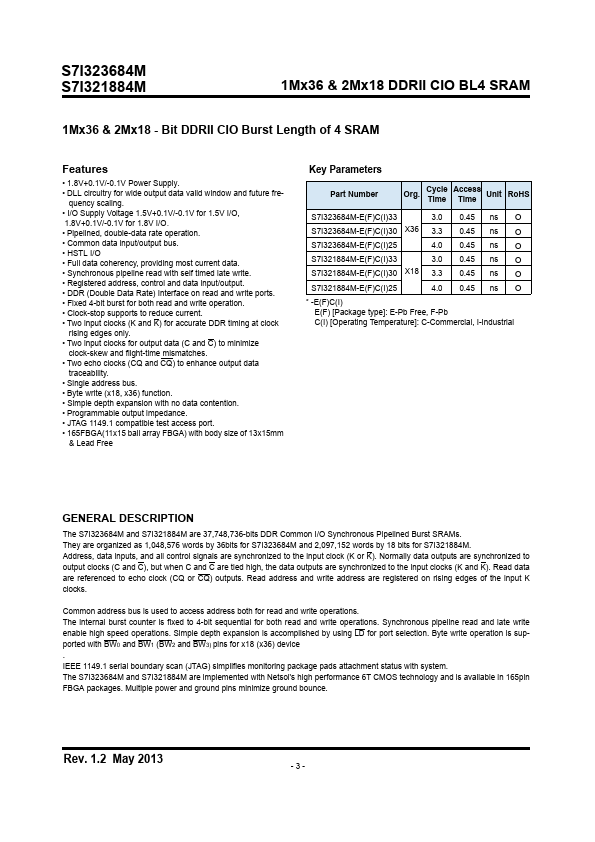

S7I321884M Description

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind. This document and all information discussed herein remain the sole and exclusive property of NETSOL.

S7I321884M Key Features

- 1.8V+0.1V/-0.1V Power Supply. -DLL circuitry for wide output data valid window and future fre

- mon data input/output bus

- HSTL I/O

- Full data coherency, providing most current data

- Synchronous pipeline read with self timed late write

- Registered address, control and data input/output

- DDR (Double Data Rate) Interface on read and write ports

- Fixed 4-bit burst for both read and write operation

- Clock-stop supports to reduce current. -Two input clocks (K and K) for accurate DDR timing at clock

- Simple depth expansion with no data contention. -Programmable output impedance