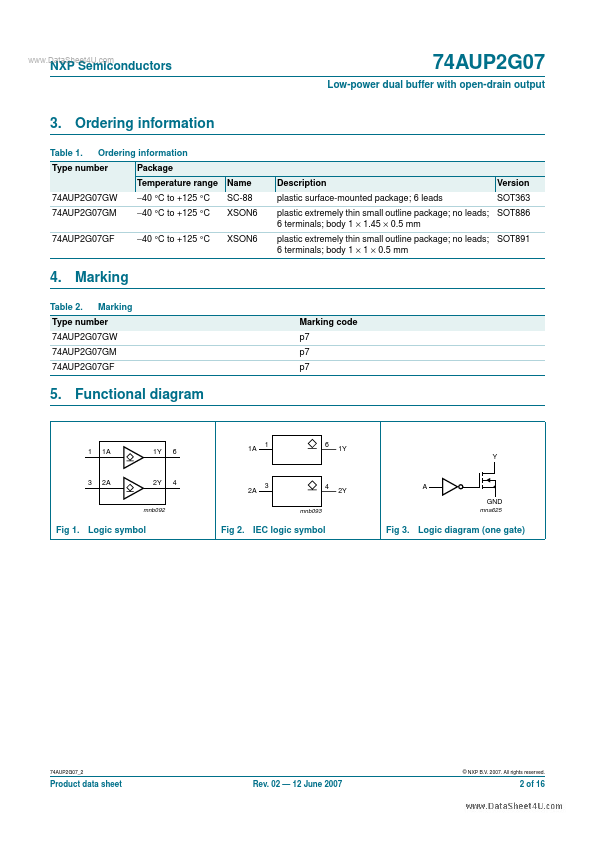

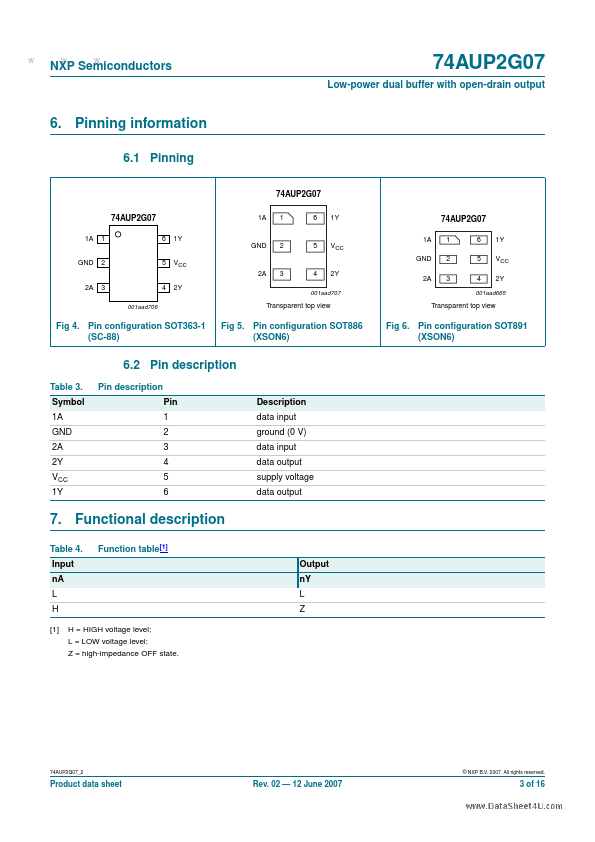

74AUP2G07 Description

The 74AUP2G07 provides two non-inverting buffers with open-drain output. The output of the device is an open drain and can be connected to other open-drain outputs to implement active-LOW wired-OR or active-HIGH wired-AND functions. Schmitt-trigger action at all inputs makes the circuit tolerant to slower input rise and fall times across the entire VCC range from 0.8 V to 3.6.

74AUP2G07 Key Features

- 12 June 2007