N04Q16YYC2B Overview

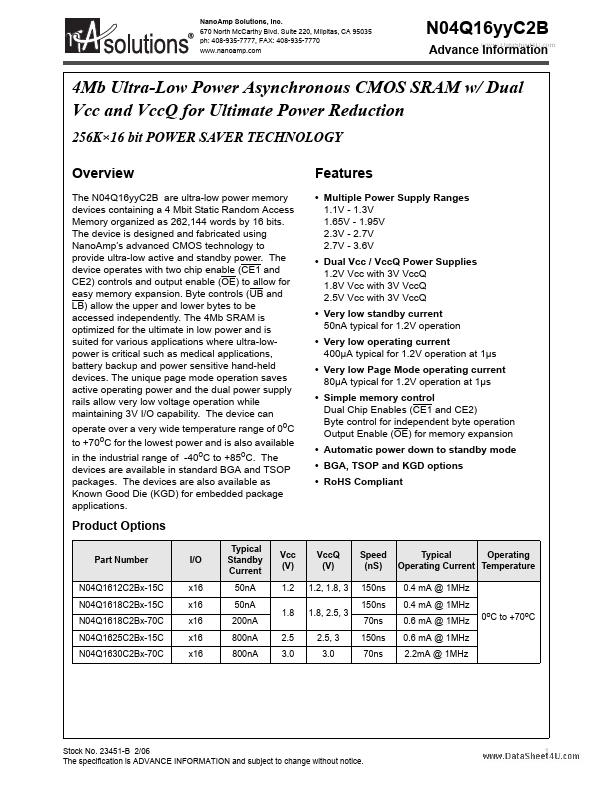

Suite 220, Milpitas, CA 95035 ph: N04Q16yyC2B Advance Information .. 4Mb Ultra-Low Power Asynchronous CMOS SRAM w/ Dual Vcc and VccQ for Ultimate Power Reduction 256K×16 bit POWER SAVER TECHNOLOGY Overview The N04Q16yyC2B are ultra-low power memory devices containing a 4 Mbit Static Random Access Memory organized as 262,144 words by 16 bits.

N04Q16YYC2B Key Features

- Multiple Power Supply Ranges 1.1V

- 1.3V 1.65V

- 1.95V 2.3V

- 2.7V 2.7V

- Dual Vcc / VccQ Power Supplies 1.2V Vcc with 3V VccQ 1.8V Vcc with 3V VccQ 2.5V Vcc with 3V VccQ

- Very low standby current 50nA typical for 1.2V operation

- Very low operating current 400µA typical for 1.2V operation at 1µs

- Very low Page Mode operating current 80µA typical for 1.2V operation at 1µs

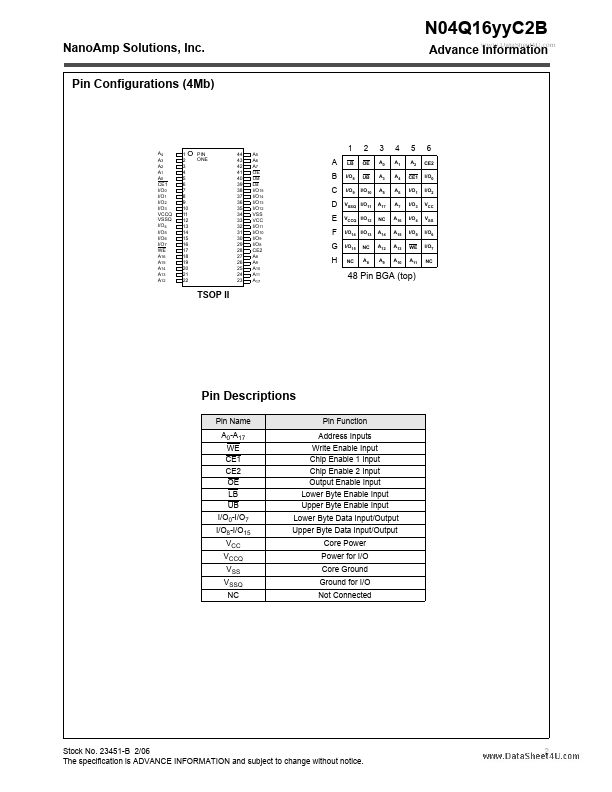

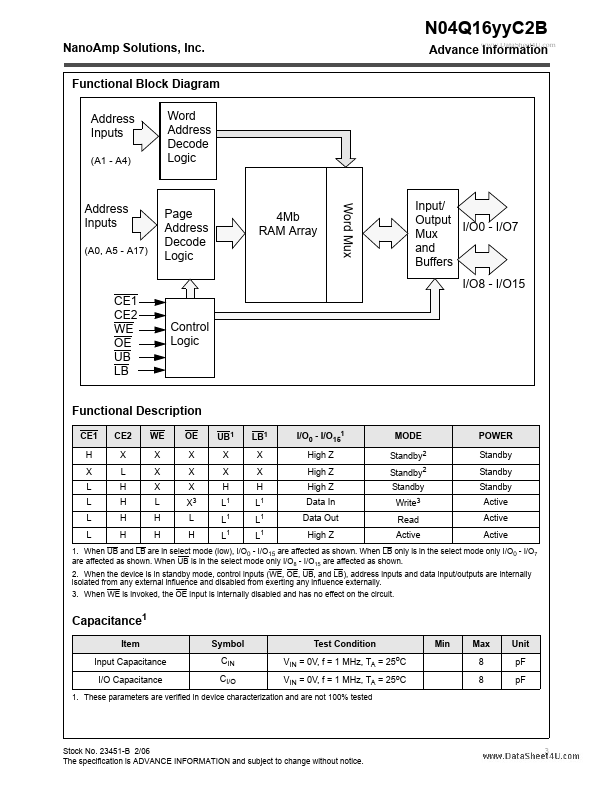

- Simple memory control Dual Chip Enables (CE1 and CE2) Byte control for independent byte operation Output Enable (OE) for

- Automatic power down to standby mode