54C165 Overview

Key Specifications

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 15 V

Min Voltage (typical range): 3 V

Description

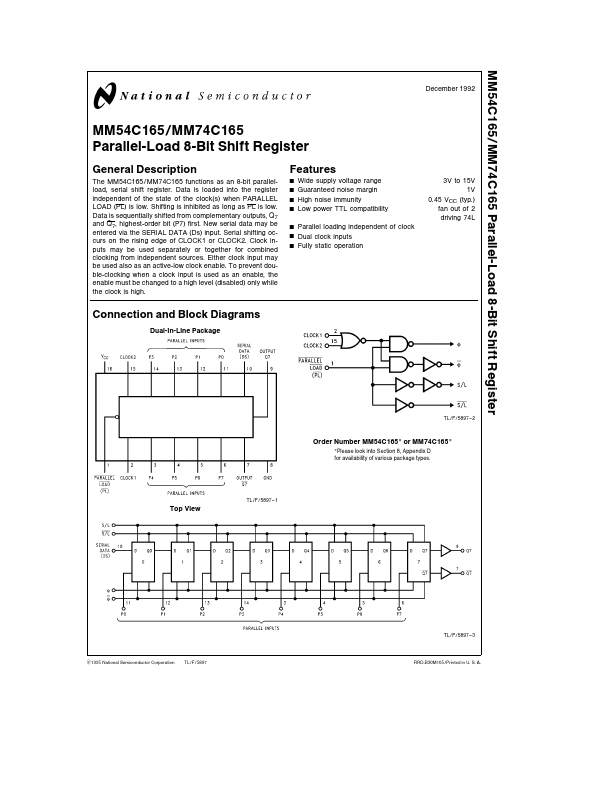

The MM54C165 MM74C165 functions as an 8-bit parallelload serial shift register Data is loaded into the register independent of the state of the clock(s) when PARALLEL LOAD (PL) is low Shifting is inhibited as long as PL is low Data is sequentially shifted from complementary outputs Q7 and Q7 highest-order bit (P7) first New serial data may be entered via the SERIAL DATA (Ds) input Serial shifting occurs on the rising edge of CLOCK1 or CLOCK2 Clock inputs may be used separately or together for combined clocking from independent sources Either clock input may be used also as an active-low clock enable To prevent double-clocking when a clock input is used as an enable the enable must be changed to a high level (disabled) only while the clock is high.