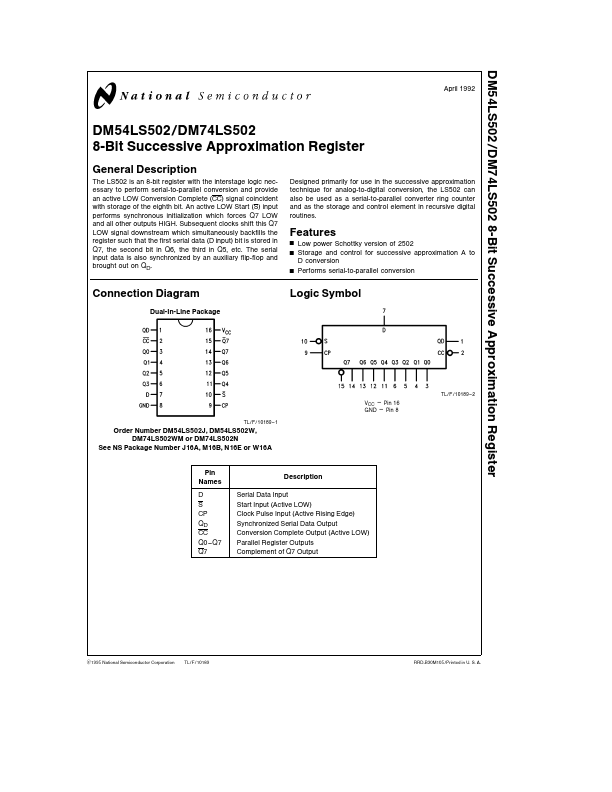

DM74LS502 Description

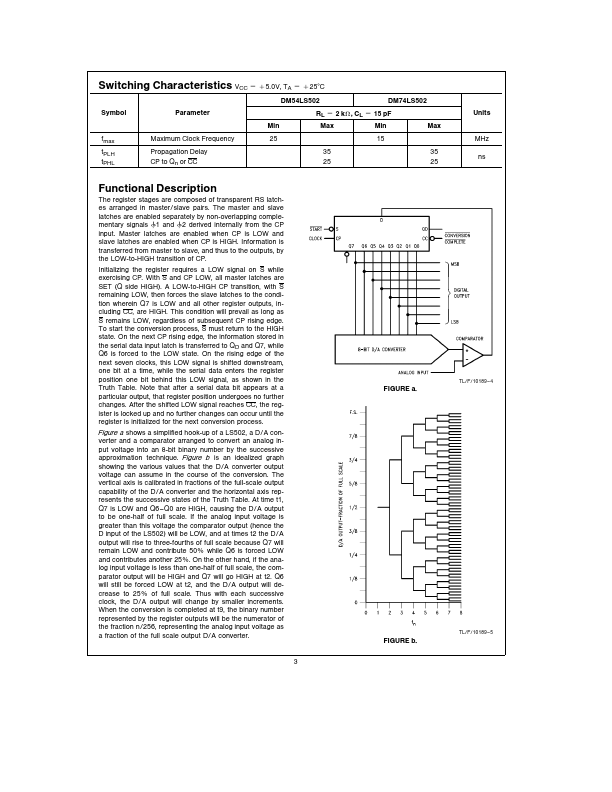

The LS502 is an 8-bit register with the interstage logic necessary to perform serial-to-parallel conversion and provide an active LOW Conversion plete (CC) signal coincident with storage of the eighth bit An active LOW Start (S) input performs synchronous initialization which forces Q7 LOW and all other outputs HIGH Subsequent clocks shift this Q7 LOW signal downstream which simultaneously backfills the register...