FPD87310 Overview

Description

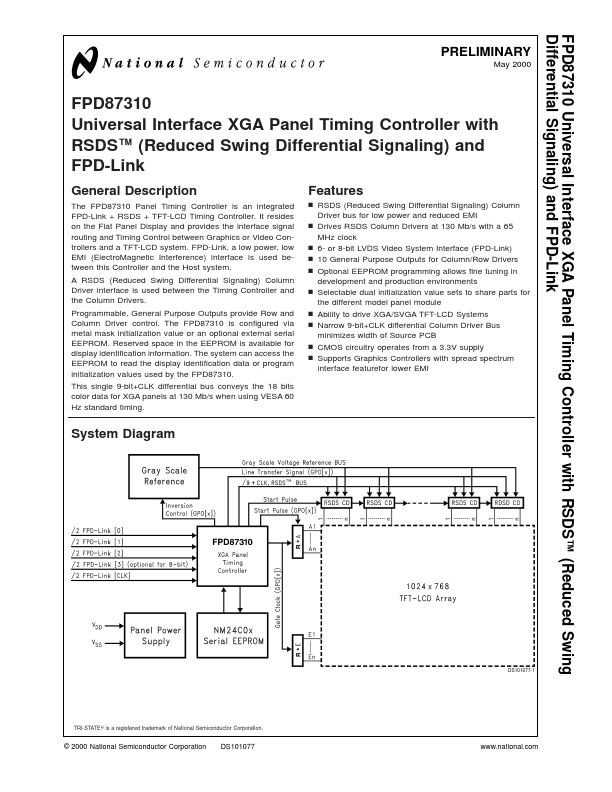

The FPD87310 Panel Timing Controller is an integrated FPD-Link + RSDS + TFT-LCD Timing Controller. It resides on the Flat Panel Display and provides the interface signal routing and Timing Control between Graphics or Video Controllers and a TFT-LCD system.

Key Features

- Optional EEPROM programming allows fine tuning in development and production environments

- Selectable dual initialization value sets to share parts for the different model panel module

- Ability to drive XGA/SVGA TFT-LCD Systems

- Narrow 9-bit+CLK differential Column Driver Bus minimizes width of Source PCB

- CMOS circuitry operates from a 3.3V supply

- Supports Graphics Controllers with spread spe