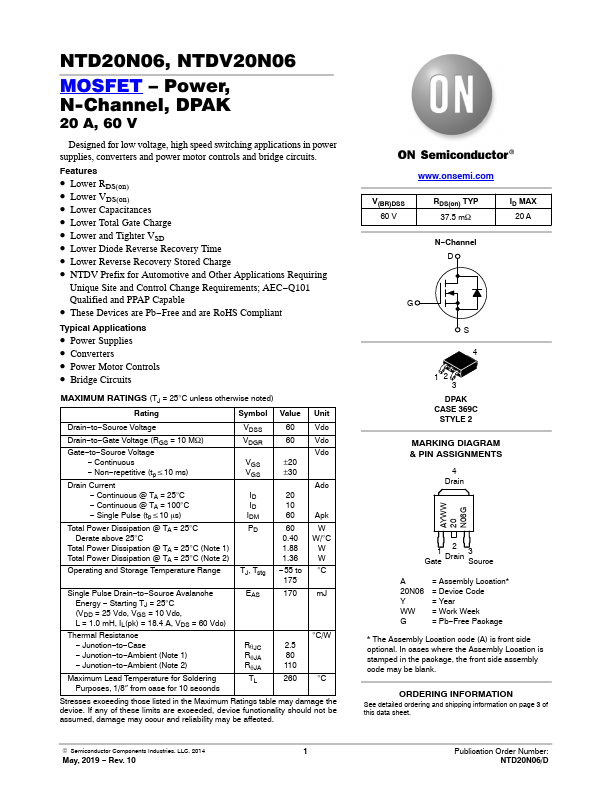

20N06

Key Features

- Lower RDS(on)

- Lower VDS(on)

- Lower Capacitances

- Lower Total Gate Charge

- Lower and Tighter VSD

- Lower Diode Reverse Recovery Time

- Lower Reverse Recovery Stored Charge

- NTDV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP Capable

- These Devices are Pb-Free and are RoHS compliant