MC100LVELT23

MC100LVELT23 is Dual Differential LVPECL to TTL Translator manufactured by onsemi.

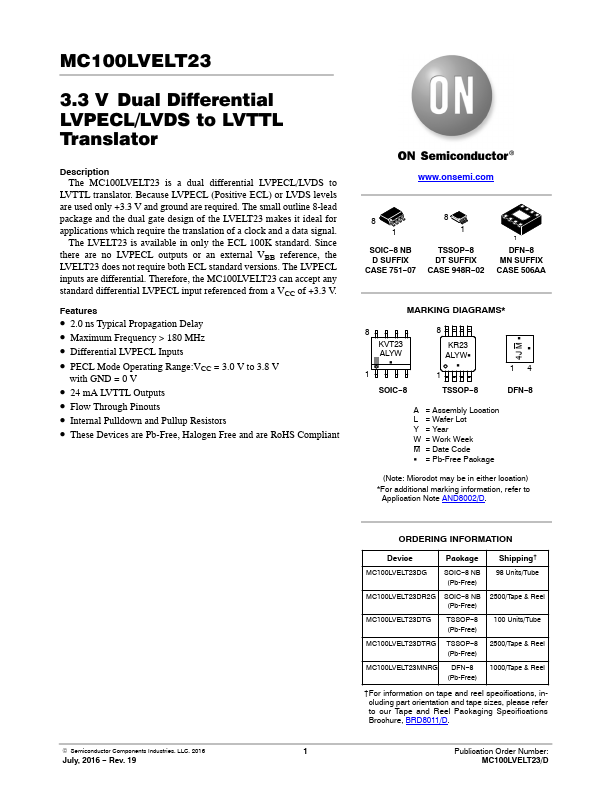

3.3 V Dual Differential LVPECL/LVDS to LVTTL Translator

Description The MC100LVELT23 is a dual differential LVPECL/LVDS to

LVTTL translator. Because LVPECL (Positive ECL) or LVDS levels are used only +3.3 V and ground are required. The small outline 8-lead package and the dual gate design of the LVELT23 makes it ideal for applications which require the translation of a clock and a data signal.

The LVELT23 is available in only the ECL 100K standard. Since there are no LVPECL outputs or an external VBB reference, the LVELT23 does not require both ECL standard versions. The LVPECL inputs are differential. Therefore, the MC100LVELT23 can accept any standard differential LVPECL...