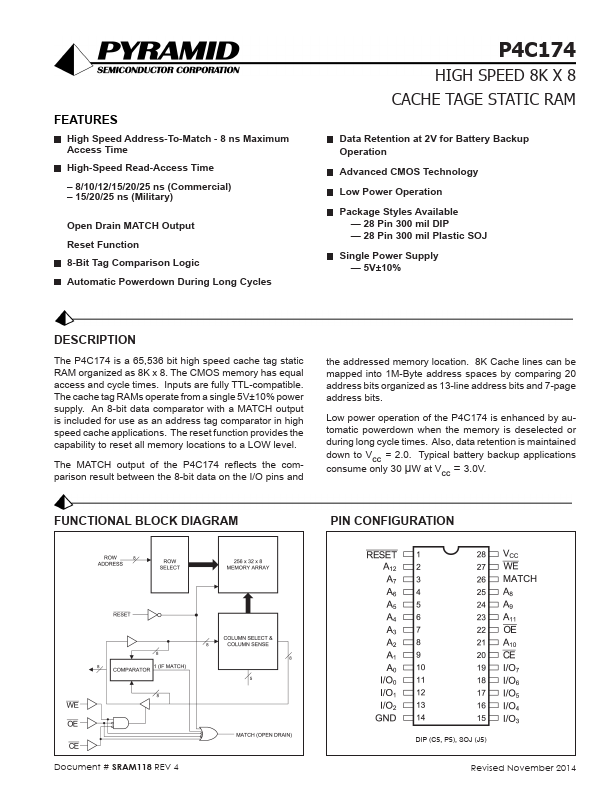

P4C174 Description

The P4C174 is a 65,536 bit high speed cache tag static RAM organized as 8K x 8. The CMOS memory has equal access and cycle times. Inputs are fully TTL-patible.

P4C174 Key Features

- 8 ns Maximum Access Time

- 8/10/12/15/20/25 ns (mercial)

- 15/20/25 ns (Military)

- 28 Pin 300 mil DIP

- 28 Pin 300 mil Plastic SOJ Single Power Supply

- 5V±10%