PE4249 Overview

Key Features

- 75-ohm impedance switch

- Non-reflective at RF1, open reflective at RF2 when OFF

- 75-ohm (0.25 watt) termination

- High isolation: 85 dB at 5 MHz, 60 dB at 1 GHz

- Low insertion loss: 0.5 dB at 5 MHz, 0.8 dB at 1 GHz

- High input IP2: >80 dBm

- CMOS/TTL single-pin control

- Single +3 volt supply operation

- Extremely low bias: 33 µA @ 3V Figure

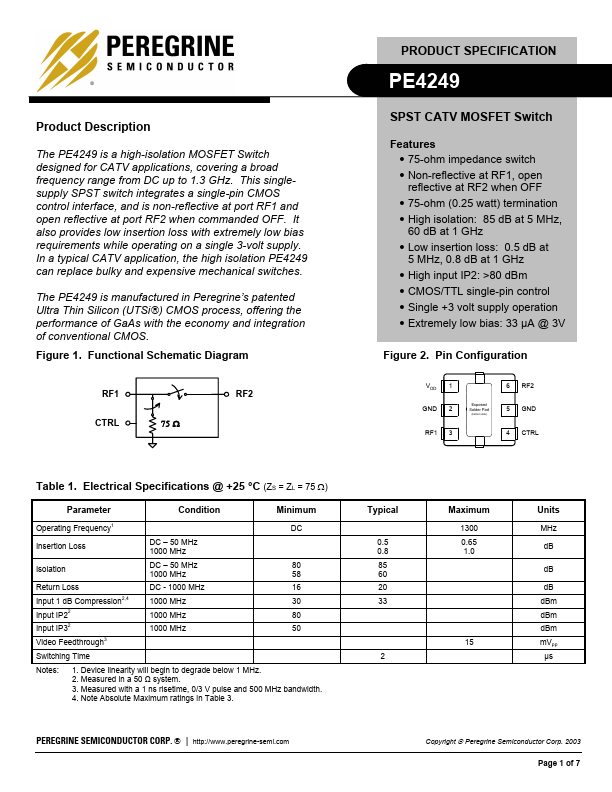

- VDD 1 GND 2 RF1 3 Exposed Solder Pad (bottom side) 6 RF2 5 GND 4 CTRL Table