PLL620-08

PLL620-08 is Low Phase Noise XO manufactured by PhaseLink.

- Part of the PLL620-05 comparator family.

- Part of the PLL620-05 comparator family.

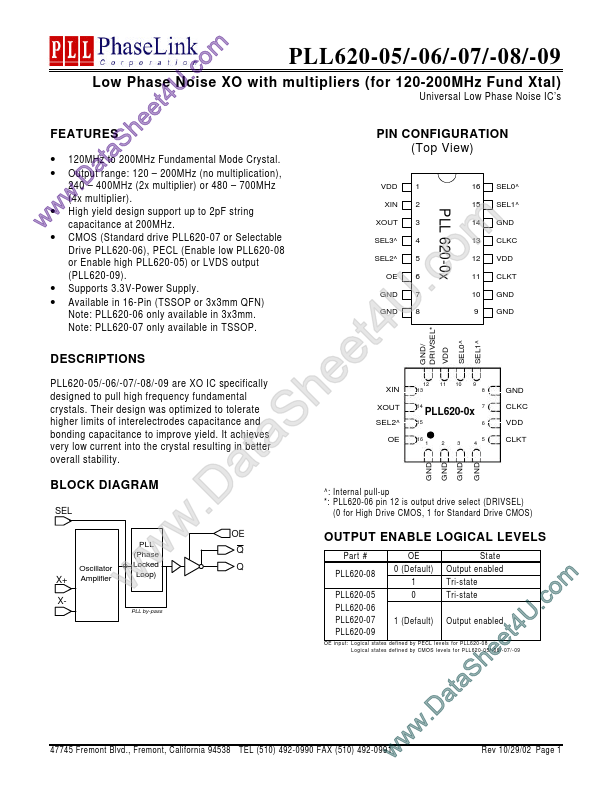

m PLL620-05/-06/-07/-08/-09 o c . XO with multipliers (for 120-200MHz Fund Xtal) Low Phase Noise U Universal Low Phase Noise IC’s 4 t e e Features h PIN CONFIGURATION S (Top View) a200MHz Fundamental Mode Crystal.

- 120MHz to t

- Output a range: 120

- 200MHz (no multiplication), D 240

- 400MHz (2x multiplier) or 480

- 700MHz . (4x multiplier). w

- w High yield design support up to 2pF string at 200MHz. w- capacitance CMOS (Standard drive PLL620-07 or Selectable

VDD 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 SEL0^ SEL1^ GND XIN

- -

GND/ DRIVSEL-

Drive PLL620-06), PECL (Enable low PLL620-08 or Enable high PLL620-05) or LVDS output (PLL620-09). Supports 3.3V-Power Supply. Available in 16-Pin...