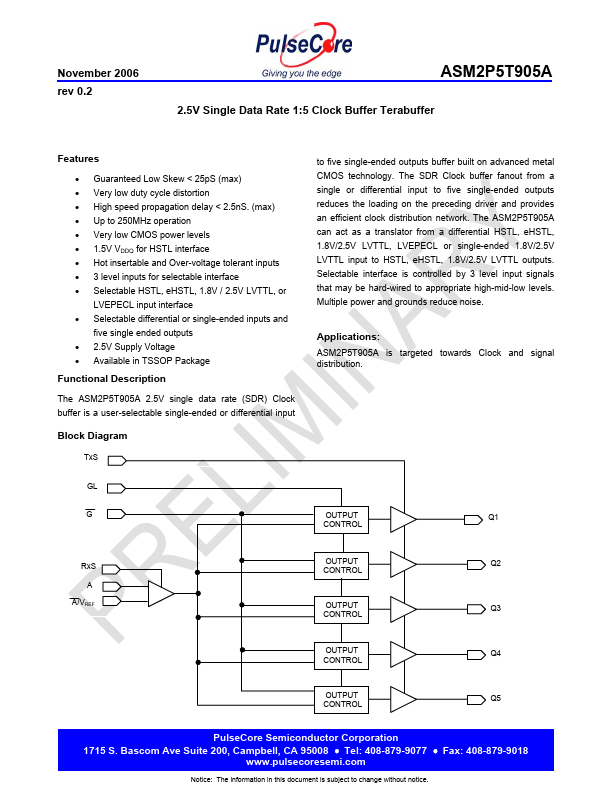

ASM2P5T905A Key Features

- Guaranteed Low Skew < 25pS (max)

- Very low duty cycle distortion

- High speed propagation delay < 2.5nS. (max)

- Up to 250MHz operation

- Very low CMOS power levels

- 1.5V VDDQ for HSTL interface

- Hot insertable and Over-voltage tolerant inputs

- 3 level inputs for selectable interface

- Selectable HSTL, eHSTL, 1.8V / 2.5V LVTTL, or

- Selectable differential or single-ended inputs and