894D115I-01

Description

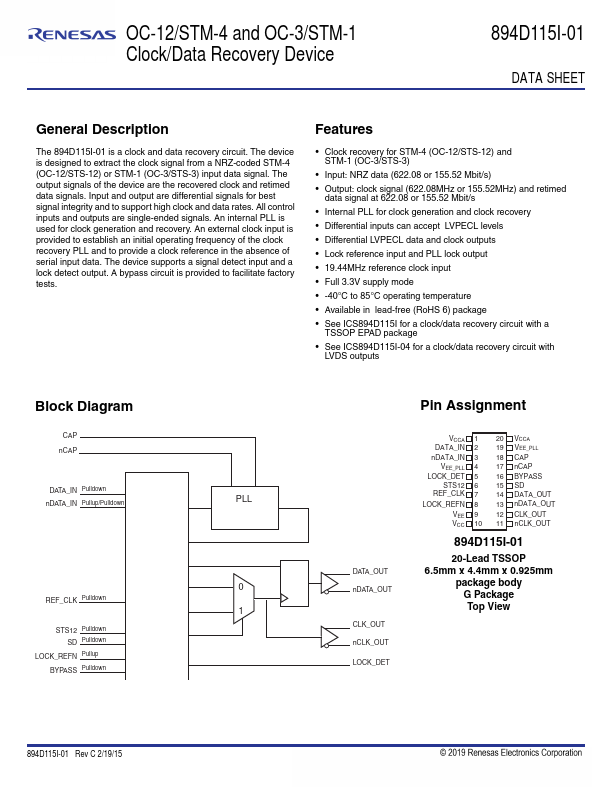

The 894D115I-01 is a clock and data recovery circuit.

Key Features

- Input: NRZ data (622.08 or 155.52 Mbit/s)

- Output: clock signal (622.08MHz or 155.52MHz) and retimed data signal at 622.08 or 155.52 Mbit/s

- Internal PLL for clock generation and clock recovery

- Differential inputs can accept LVPECL levels

- Differential LVPECL data and clock outputs

- Lock reference input and PLL lock output

- 19.44MHz reference clock input

- Full 3.3V supply mode

- 40°C to 85°C operating temperature

- Available in lead-free (RoHS