IDT72251

Overview

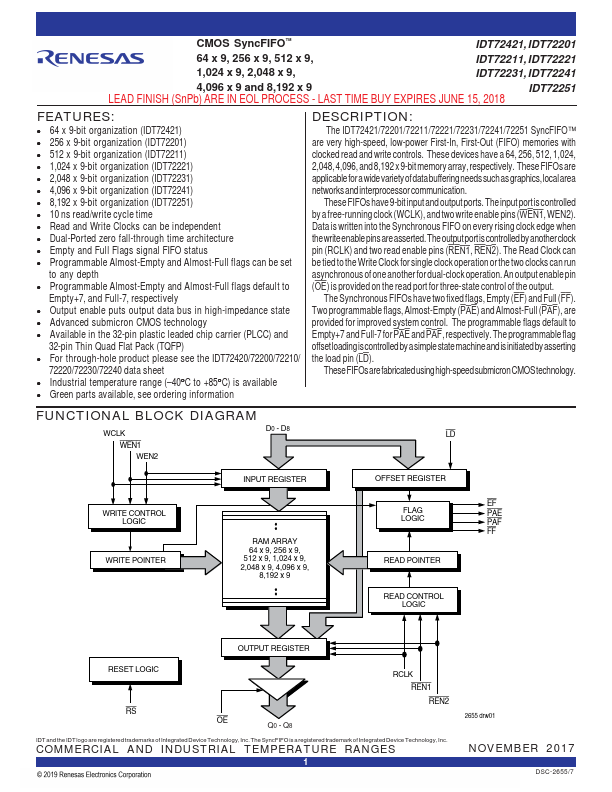

The IDT72421/72201/72211/72221/72231/72241/72251 SyncFIFO™ are very high-speed, low-power First-In, First-Out (FIFO) memories with clocked read and write controls. These devices have a 64, 256, 512, 1,024, 2,048, 4,096, and 8,192 x 9-bit memory array, respectively.

- 64 x 9-bit organization (IDT72421)

- 256 x 9-bit organization (IDT72201)

- 512 x 9-bit organization (IDT72211)

- 1,024 x 9-bit organization (IDT72221)

- 2,048 x 9-bit organization (IDT72231)

- 4,096 x 9-bit organization (IDT72241)

- 8,192 x 9-bit organization (IDT72251)

- 10 ns read/write cycle time

- Read and Write Clocks can be independent

- Dual-Ported zero fall-through time architecture