IDT72V85

Description

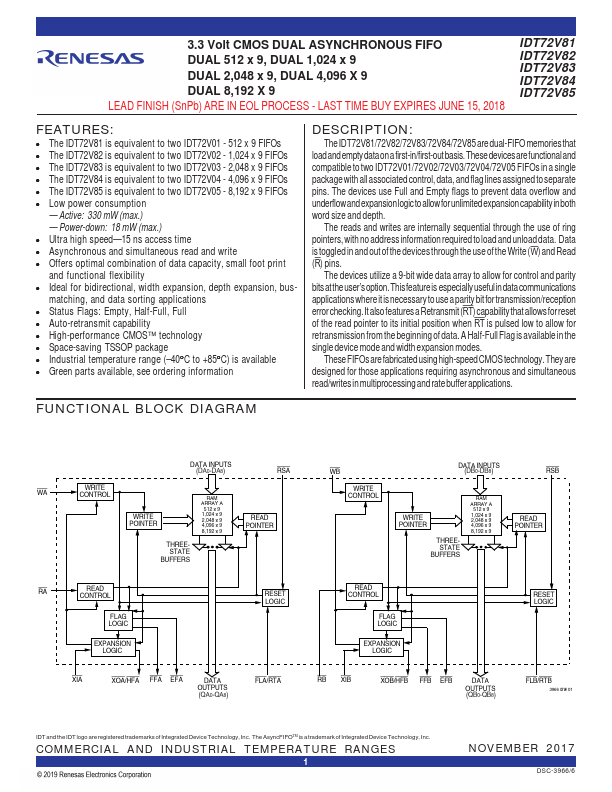

The IDT72V81/72V82/72V83/72V84/72V85 are dual-FIFO memories that load and empty data on a first-in/first-out basis.

Key Features

- Low power consumption

- Ultra high speed—15 ns access time

- Asynchronous and simultaneous read and write

- Offers optimal bination of data capacity, small foot print and functional flexibility

- Ideal for bidirectional, width expansion, depth expansion, busmatching, and data sorting applications

- Status Flags: Empty, Half-Full, Full

- Auto-retransmit capability

- High-performance CMOS™ technology

- Space-saving TSSOP package

- Industrial temperature range (–40°C to +85°C) is available