Datasheet Summary

..

Renesas LSIs

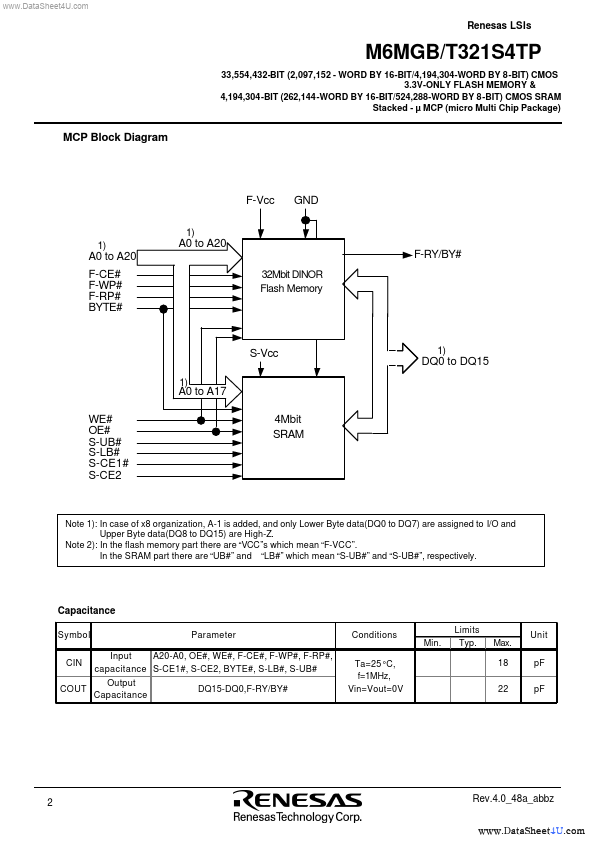

M6MGB/T321S4TP

33,554,432-BIT (2,097,152

- WORD BY 16-BIT/4,194,304-WORD BY 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY & 4,194,304-BIT (262,144-WORD BY 16-BIT/524,288-WORD BY 8-BIT) CMOS SRAM Stacked

- µ MCP (micro Multi Chip Package)

Description

M6MGB/T321S4TP provides for Software Lock Release function. Usually, all memory blocks are locked and can not be programmed or erased, when F-WP# is low. Using Software Lock Release function, program or erase operation 32M-bit Flash memory is a 4,194,304 bytes / 2,097,152 words, can be executed. 3.3V-only, and high performance non-volatile memory fabricated by CMOS technology for the peripheral circuit and...