RC38312

Overview

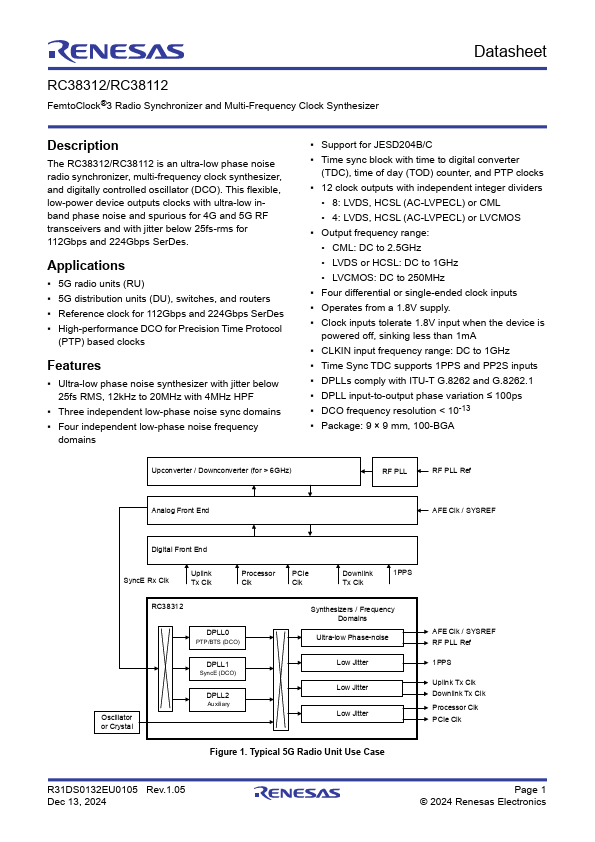

The RC38312/RC38112 is an ultra-low phase noise radio synchronizer, multi-frequency clock synthesizer, and digitally controlled oscillator (DCO). This flexible, low-power device outputs clocks with ultra-low inband phase noise and spurious for 4G and 5G RF transceivers and with jitter below 25fs-rms for 112Gbps and 224Gbps SerDes.

- 8: LVDS, HCSL (AC-LVPECL) or CML

- 4: LVDS, HCSL (AC-LVPECL) or LVCMOS; Output frequency range:

- CML: DC to 2.5GHz

- LVDS or HCSL: DC to 1GHz

- LVCMOS: DC to 250MHz; Four differential or single-ended clock inputs; Operates from a 1.8V supply.; Clock inputs tolerate 1.8V input when the device is powered off, sinking less than 1mA; CLKIN input frequency range: DC to 1GHz; Time Sync TDC supports 1PPS and PP2S inputs; DPLLs comply with ITU-T G.8262 and G.8262.1; DPLL input-to-output phase variation ≤ 100ps; DCO frequency resolution < 10-13; Package: 9 × 9 mm, 100-BGA Upconverter / Downconverter (for > 6GHz) RF PLL RF PLL Ref Analog Front End AFE Clk / SYSREF Digital Front End SyncE Rx Clk Uplink Tx Clk Processor Clk PCIe Clk Downlink Tx Clk 1PPS RC38312 Oscillator or Crystal DPLL0