UPD48011318 Overview

Key Specifications

Pins: 180

Operating Voltage: 1.5 V

Max Voltage (typical range): 1.605 V

Min Voltage (typical range): 1.395 V

Description

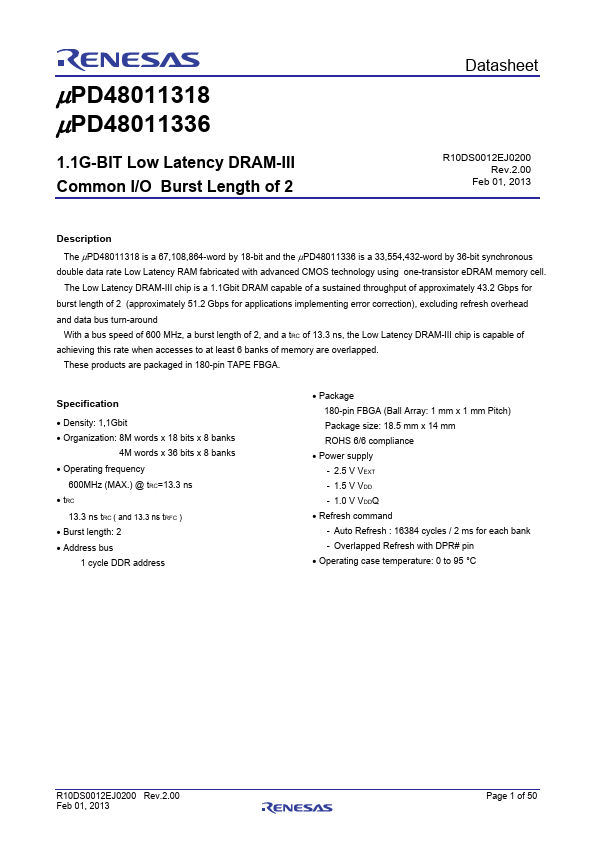

The μPD48011318 is a 67,108,864-word by 18-bit and the μPD48011336 is a 33,554,432-word by 36-bit synchronous double data rate Low Latency RAM fabricated with advanced CMOS technology using one-transistor eDRAM memory cell. The Low Latency DRAM-III chip is a 1.1Gbit DRAM capable of a sustained throughput of approximately 43.2 Gbps for burst length of 2 (approximately 51.2 Gbps for applications implementing error correction), excluding refresh overhead and data bus turn-around With a bus speed of 600 MHz, a burst length of 2, and a tRC of 13.3 ns, the Low Latency DRAM-III chip is capable of achieving this rate when accesses to at least 6 banks of memory are overlapped.

Key Features

- 1 cycle 600MHz DDR Muxed Address

- Optional data bus inversion to reduce SSO, SSN, maximum I/O current, and average I/O power

- Training sequence for per-bit deskew

- Selectable Refresh Mode: Auto or Overlapped Refresh

- Programmable PVT-compensated output impedance