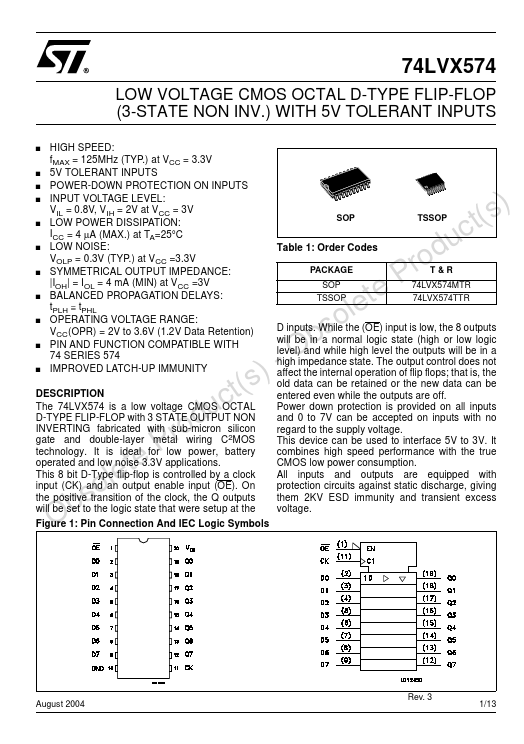

74LVX574 Overview

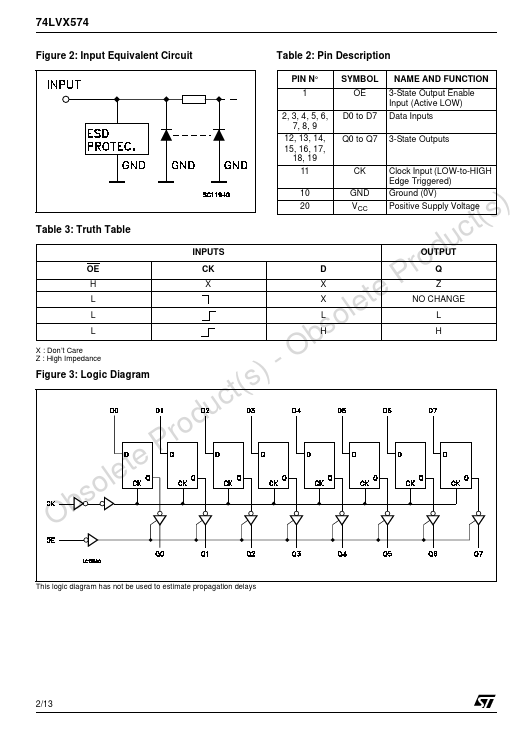

c The 74LVX574 is a low voltage CMOS OCTAL u D-TYPE FLIP-FLOP with 3 STATE OUTPUT NON d INVERTING fabricated with sub-micron silicon ro gate and double-layer metal wiring C2MOS P technology. It is ideal for low power, battery te operated and low noise 3.3V applications. This 8 bit D-Type flip-flop is controlled by a clock le input (CK) and an output enable input (OE).