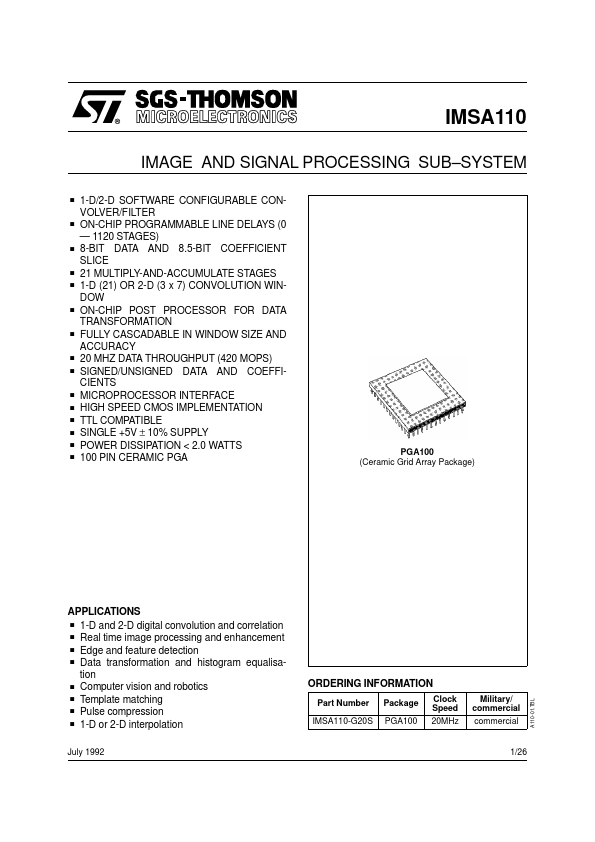

| Part | IMSA110 |

|---|---|

| Description | IMAGE AND SIGNAL PROCESSING SUB.SYSTEM |

| Manufacturer | STMicroelectronics |

| Size | 354.67 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| ATC2603 | Actions | integrated audio and power management subsystem IC |

| LM78S40 | National Semiconductor | Universal Switching Regulator Subsystem |

| AD607 | Analog Devices | Low Power Mixer/AGC/RSSI 3 V Receiver IF Subsystem |