M74HC109 Overview

Description

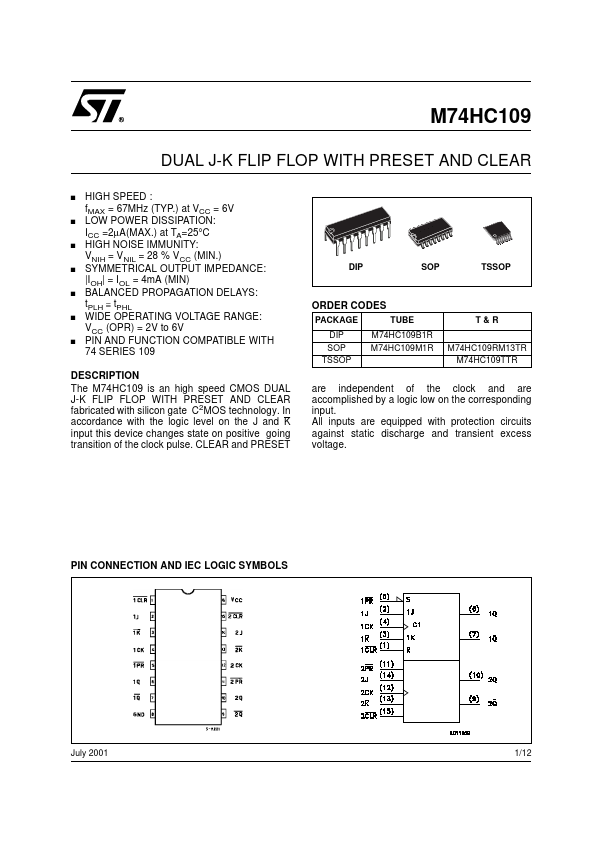

The M74HC109 is an high speed CMOS DUAL J-K FLIP FLOP WITH PRESET AND CLEAR fabricated with silicon gate C2MOS technology. In accordance with the logic level on the J and K input this device changes state on positive going transition of the clock pulse.