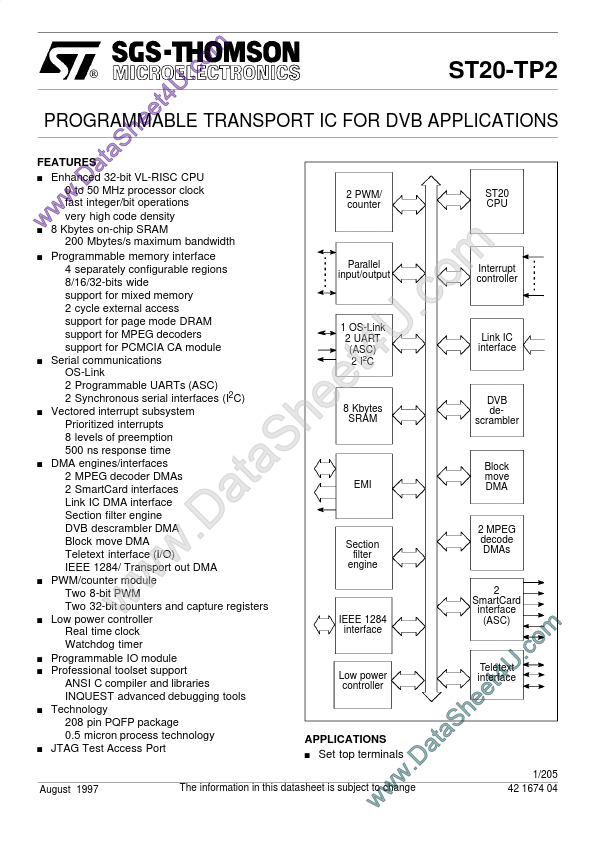

- Part: ST20TP2BX50S

- Description: Programmable Transport IC

- Manufacturer: STMicroelectronics

- Size: 1.08 MB

Related STMicroelectronics Datasheets

| Part Number | Description |

|---|---|

| ST20-C1 | Instruction Set Reference Manual |

| ST20-GP1 | GPS PROCESSOR |

| ST20-GP6 | GPS PROCESSOR |

| ST20-JPI | PC PARALLEL PORT TO JTAG INTERFACE |

| ST20-PPI | PC PARALLEL PORT TO OS-LINK INTERFACE |