SK10E142 Overview

Key Features

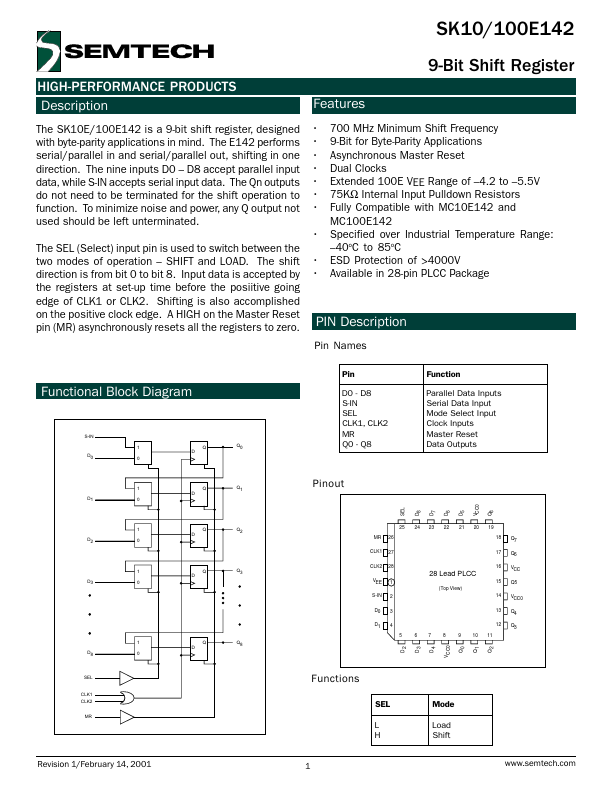

- D8 accept parallel input data, while S-IN accepts serial input data. The Qn outputs do not need to be terminated for the shift operation to function. To minimize noise and power, any Q output not used should be left unterminated. The SEL (Select) input pin is used to switch between the two modes of operation

- SHIFT and LOAD. The shift direction is from bit 0 to bit 8. Input data is accepted by the registers at set-up time before the posiitive going edge of CLK1 or CLK2. Shifting is also accomplished on the positive clock edge. A HIGH on the Master Reset pin (MR) asynchronously resets all the registers to zero