74HC595

Key Features

- Output Drive Capability: 15 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 to 6.0 V

- Low Input Current: 1.0 mA

- High Noise Immunity Characteristic of CMOS Devices

- In pliance with the Requirements Defined by JEDEC

- ESD Performance: HBM > 2000 V; Machine Model > 200 V

- Chip plexity: 328 FETs or 82 Equivalent Gates

- Improvements over HC595

- These are Pb−Free Devices

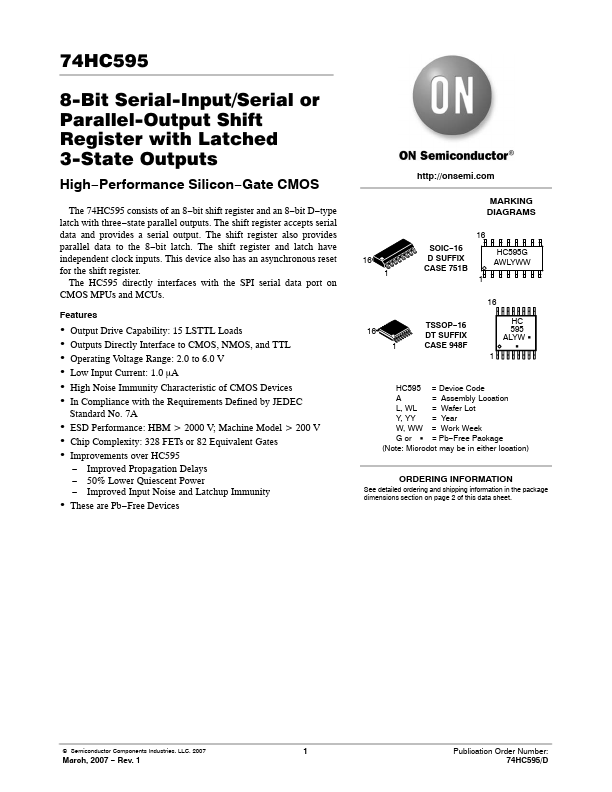

Representative 74HC595 image (package may vary by manufacturer)