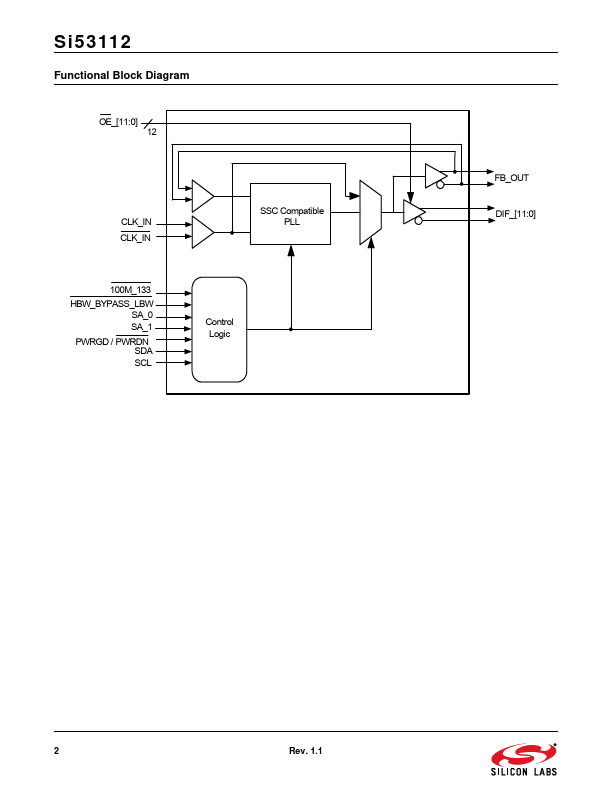

SI53112 Key Features

- Twelve 0.7 V low-power, push

- PLL or bypass mode

- Spread spectrum tolerable

- 1.05 to 3.3 V I/O supply voltage

- 50 ps output-to-output skew

- PLL bandwidth SW SMBUS programming overrides the latch

- Gen 3 SRNS pliant

- 100 ps input-to-output delay

- For higher output devices or