SI531

Overview

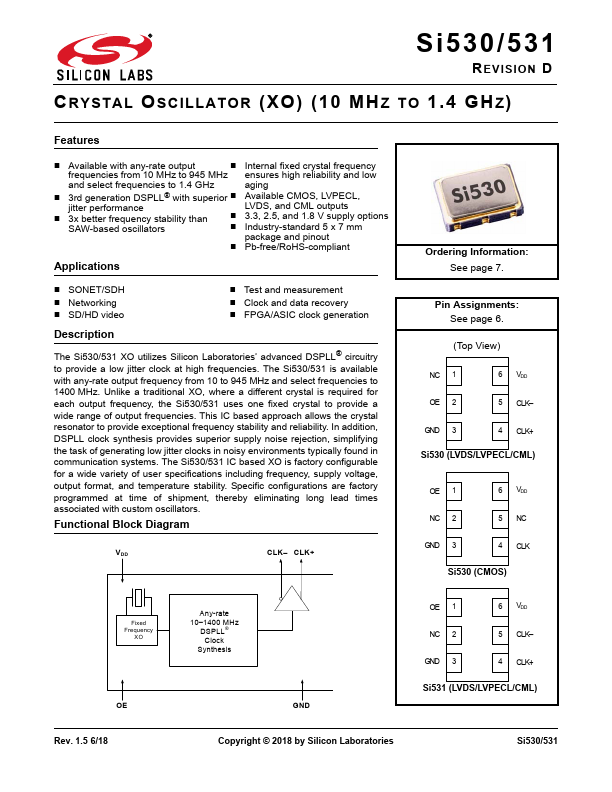

The Si530/531 XO utilizes Silicon Laboratories’ advanced DSPLL® circuitry to provide a low jitter clock at high frequencies. The Si530/531 is available with any-rate output frequency from 10 to 945 MHz and select frequencies to 1400 MHz.

- frequencies from 10 MHz to 945 MHz and select frequencies to 1.4 GHz

- 3rd generation DSPLL® with superior

- jitter performance *

- 3x better frequency stability than

- SAW-based oscillators

- Internal fixed crystal frequency ensures high reliability and low aging Available CMOS, LVPECL, LVDS, and CML outputs 3.3, 2.5, and 1.8 V supply options Industry-standard 5 x 7 mm package and pinout

- Pb-free/RoHS-compliant Si5602