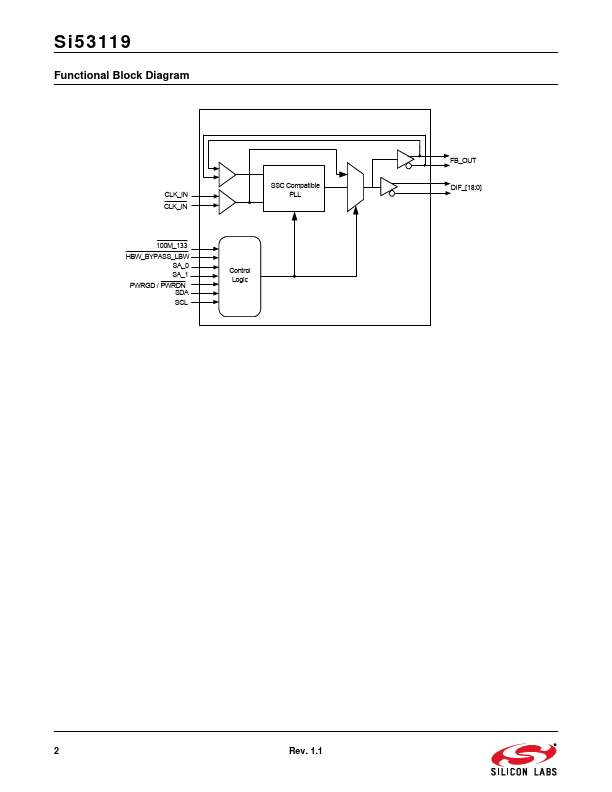

SI53119 Key Features

- Nineteen 0.7 V low-power, push

- PLL or bypass mode

- Spread spectrum tolerable

- 100 MHz /133 MHz PLL

- 1.05 to 3.3 V I/O supply voltage

- operation, supports PCIe and QPI

- PLL bandwidth SW SMBUS programming overrides the latch

- Extended Temperature

- 40 to 85 °C

- Separate VDDIO for outputs