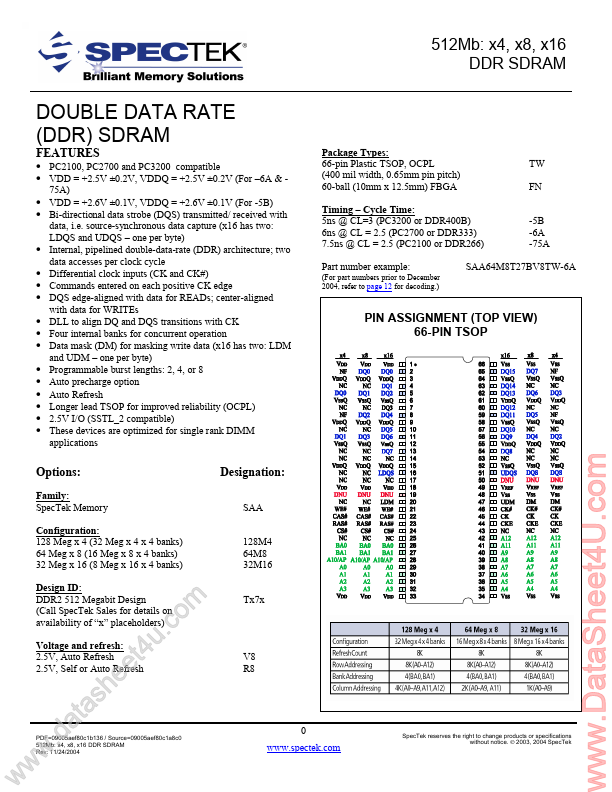

SAA128M4T27B

Overview

- PC2100, PC2700 and PC3200 compatible

- VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V (For -6A & 75A)

- VDD = +2.6V ±0.1V, VDDQ = +2.6V ±0.1V (For -5B)

- Bi-directional data strobe (DQS) transmitted/ received with data, i.e. source-synchronous data capture (x16 has two: LDQS and UDQS - one per byte)

- Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- Commands entered on each positive CK edge

- DQS edge-aligned with data for READs; center-aligned with data for WRITEs

- DLL to align DQ and DQS transitions with CK

- Four internal banks for concurrent operation