P16M648YA7

Key Features

- PC-100 and PC133 Compatible

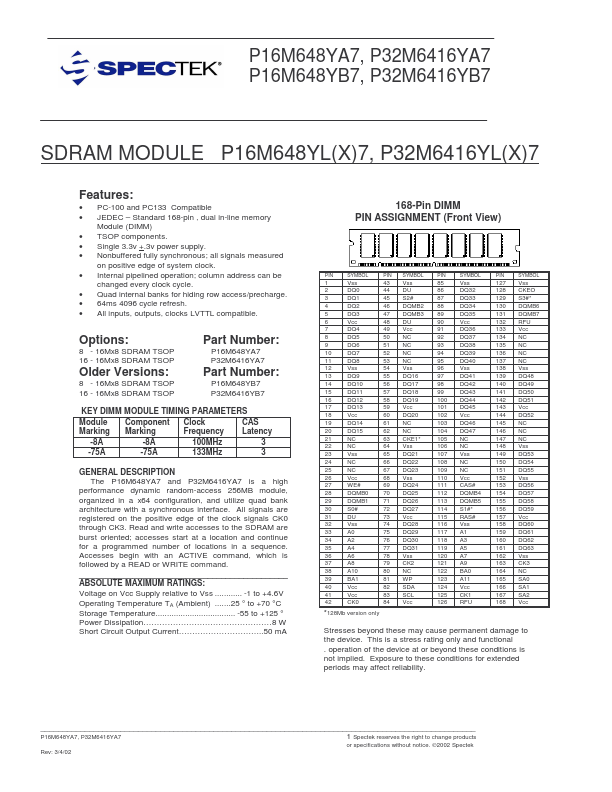

- JEDEC - Standard 168-pin , dual in-line memory Module (DIMM)

- TSOP components.

- Single 3.3v +.3v power supply.

- Nonbuffered fully synchronous; all signals measured on positive edge of system clock.

- Internal pipelined operation; column address can be changed every clock cycle.

- Quad internal banks for hiding row access/precharge.

- 64ms 4096 cycle refresh.

- All inputs, outputs, clocks LVTTL compatible. Options: 8 - 16Mx8 SDRAM TSOP 16 - 16Mx8 SDRAM TSOP Older Versions: 8 - 16Mx8 SDRAM TSOP 16 - 16Mx8 SDRAM TSOP Part Number: