TSC73M2910A

TSC73M2910A is Microcontroller manufactured by TDK Corporation.

- Part of the TSC73M2910 comparator family.

- Part of the TSC73M2910 comparator family.

TSC 73M2910/2910A

Microcontroller

DESCRIPTION

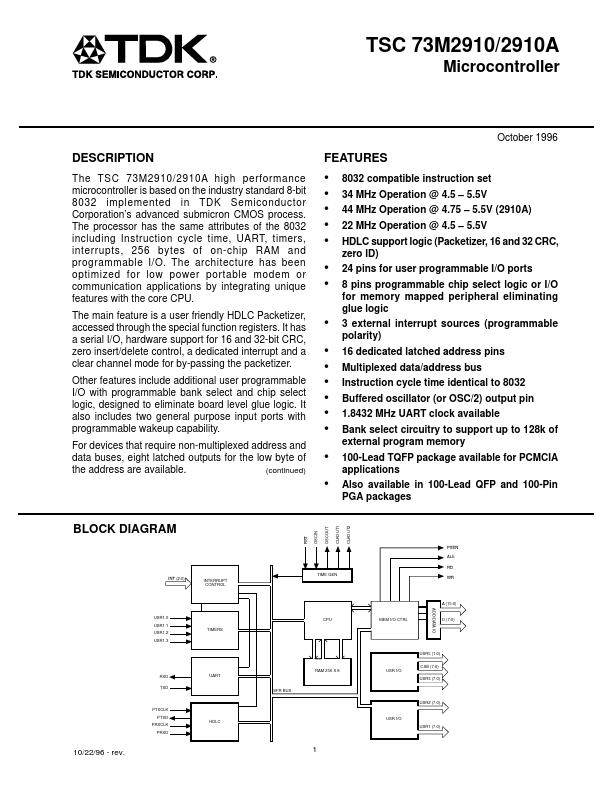

The TSC 73M2910/2910A high performance microcontroller is based on the industry standard 8-bit 8032 implemented in TDK Semiconductor Corporation’s advanced submicron CMOS process. The processor has the same attributes of the 8032 including Instruction cycle time, UART, timers, interrupts, 256 bytes of on-chip RAM and programmable I/O. The architecture has been optimized for low power portable modem or munication applications by integrating unique Features with the core CPU.

The main feature is a user friendly HDLC Packetizer, accessed through the special function registers. It has a serial I/O, hardware support for 16 and 32-bit CRC, zero insert/delete control, a dedicated interrupt and a clear channel mode for by-passing the packetizer.

Other Features include additional user programmable I/O with programmable bank select and chip select logic, designed to eliminate board level glue logic. It also includes two general purpose...