TC554161TRL-70L

Description

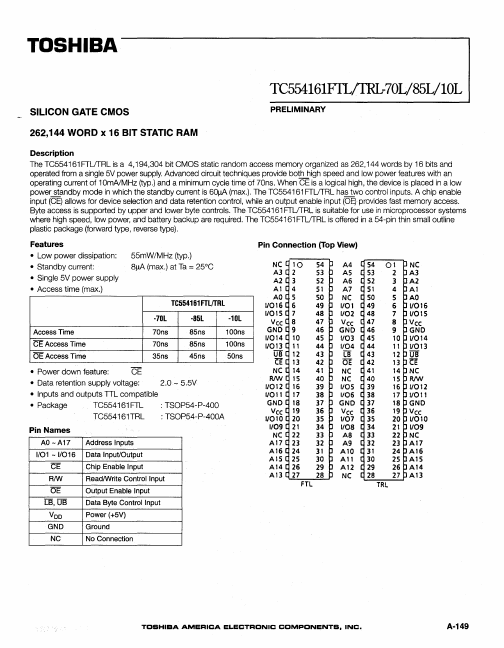

The TC554161 FTUf RL is a 4,194,304 bit CMOS static random access memory organized as 262,144 words by 16 bits and operated from a single 5V power supply. Advanced circuit techniques provide both high speed and low power features with an operating current of 10m NMHz (typ.) and a minimum cycle time of 70ns. When CE is a logical high, the device is placed in a low power standby mode in which the standby current is 601-!A (max.). The TC554161 FTUf RL has two control inputs. A chip enable input (CE) allows for device selection and data retention control, while an output enable input (OE) provides fast memory access. Byte access is supported by upper and lower byte controls. The TC554161 FTUf RL is suitable for use in microprocessor systems where high speed, low power, and battery backup are required. The TC554161 FTUf RL is offered in a 54-pin thin small outline plastic...