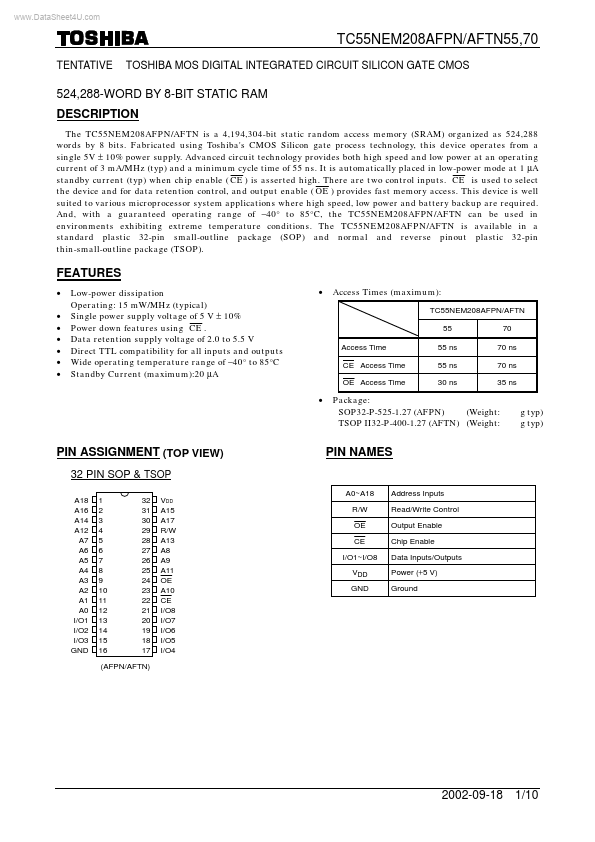

TC55NEM208AFPN Key Features

- Low-power dissipation Operating: 15 mW/MHz (typical) Single power supply voltage of 5 V ± 10% Power down features using

- Access Times (maximum)

- Package: SOP32-P-525-1.27 (AFPN) (Weight: TSOP II32-P-400-1.27 (AFTN) (Weight

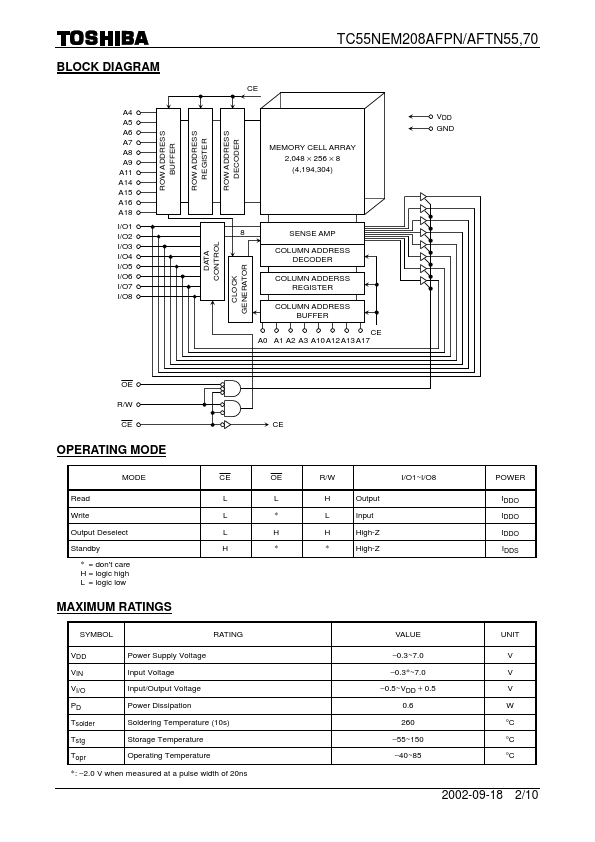

- = don't care H = logic high L = logic low

- R/W H L H

- I/O1~I/O8 Output Input High-Z High-Z

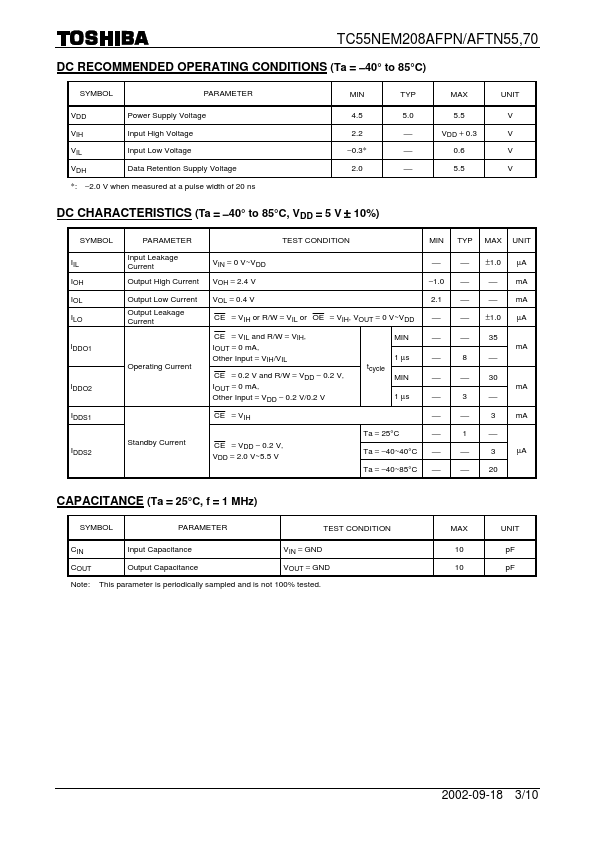

- MAXIMUM RATINGS