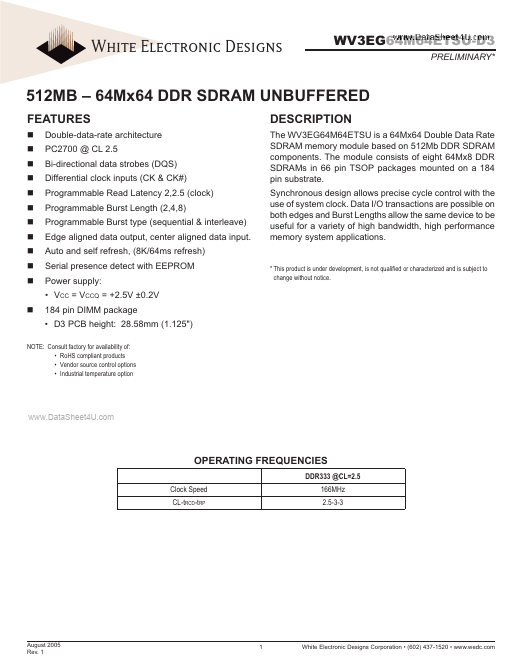

WV3EG64M64ETSU-D3 Description

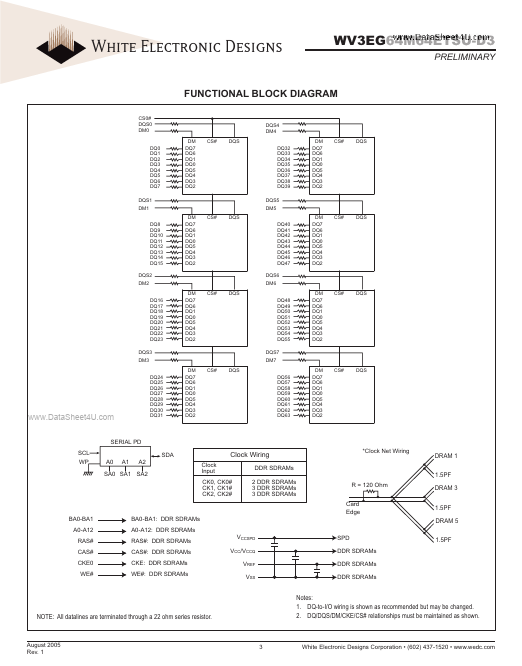

The WV3EG64M64ETSU is a 64Mx64 Double Data Rate SDRAM memory module based on 512Mb DDR SDRAM ponents. The module consists of eight 64Mx8 DDR SDRAMs in 66 pin TSOP packages mounted on a 184 pin substrate. Synchronous design allows precise cycle control with the use of system clock.

WV3EG64M64ETSU-D3 Key Features

- VCC = VCCQ = +2.5V ±0.2V 184 pin DIMM package

- D3 PCB height: 28.58mm (1.125")

- RoHS pliant products

- Vendor source control options

- Industrial temperature option

- This product is under development, is not qualified or characterized and is subject to change without notice