MT9046

Description

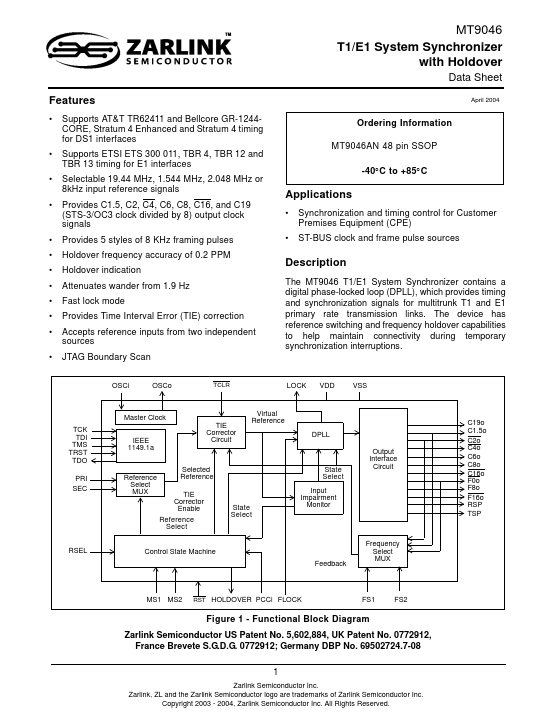

The MT9046 T1/E1 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing and synchronization signals for multitrunk T1 and E1 primary rate transmission links.

Applications

- Synchronization and timing control for Customer Premises Equipment (CPE) ST-BUS clock and frame pulse sources