Datasheet Summary

..

PDSP16488A MA

PDSP16488A MA

Single Chip 2D Convolver with Integral Line Delays

Supersedes January 1997 version, DS3742

- 3.1 DS3742

- 5.0 November 2000

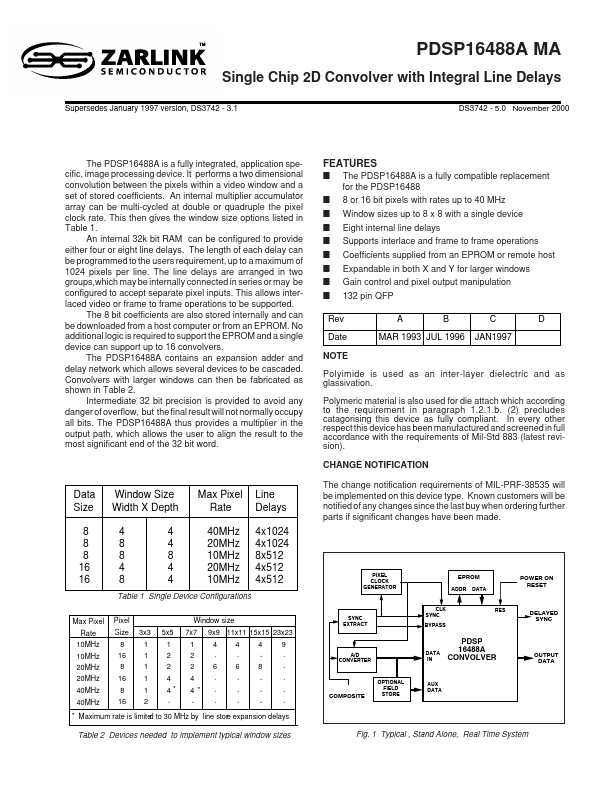

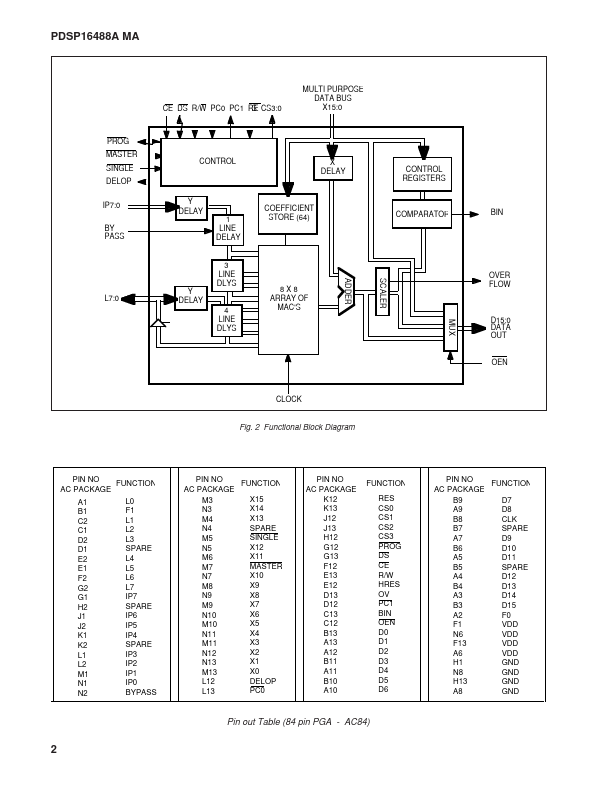

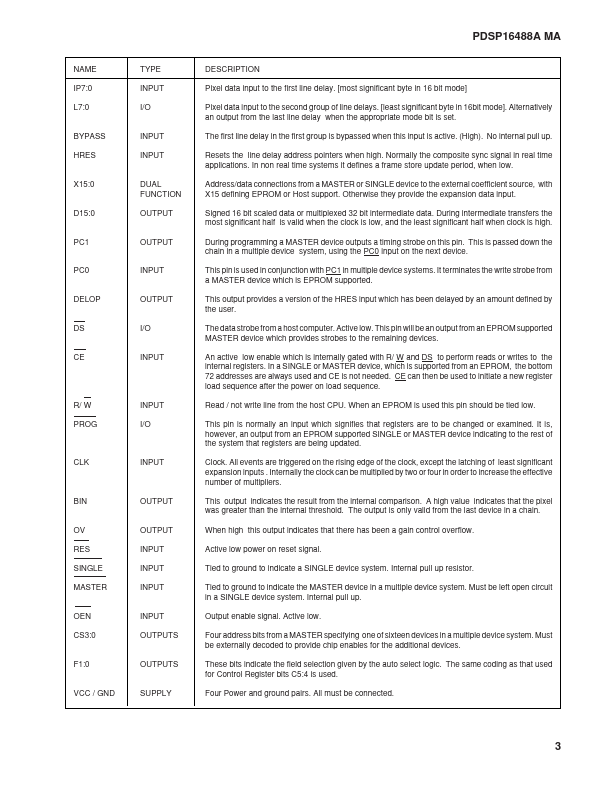

The PDSP16488A is a fully integrated, application specific, image processing device. It performs a two dimensional convolution between the pixels within a video window and a set of stored coefficients. An internal multiplier accumulator array can be multi-cycled at double or quadruple the pixel clock rate. This then gives the window size options listed in Table 1. An internal 32k bit RAM can be configured to provide either four or eight line delays. The length of each delay can be programmed to the users requirement,...